Polar IP

Welcome to the ultimate Polar IP hub! Explore our vast directory of Polar IP

All offers in

Polar IP

Filter

Compare

10

Polar IP

from

10

vendors

(1

-

10)

-

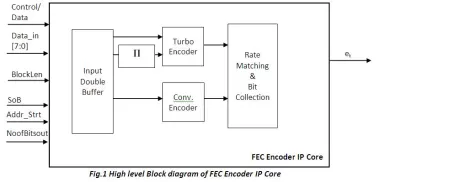

Complete FEC Encoder Solution compliant to LTE/ LTE A Specification

- Controlled selection of Turbo or Convolution path (based on data blocks input or control data input)

- Rate 1/3 tail biting Convolution encoder

- Rate 1/3 turbo encoder

- Rate matching for Turbo coded transport channels

-

5G Polar Intel® FPGA IP

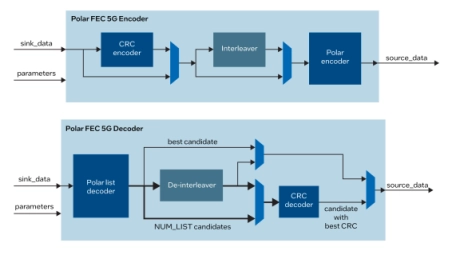

- The 5G Polar Intel® FPGA IP implements a forward error correction (FEC) encoder and decoder based on polar codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration into your wireless design

- Polar codes represent an emerging class of error correction supporting the high throughput requirements for 5G new radio (NR).

-

Polar Encoder / Decoder for 5G NR control channels

- The Polar core uses PC- and CRC-aided Successive Cancellation List decoding to achieve compromise-free error correction performance.

- Parallelism, latency, throughput and decoder list size are all configurable at synthesis time - including reducing list size below the standard list 8 - giving programme teams precise control over the power and performance trade-off for each target application.

-

5G Polar Decoder

- High performance in low SNR

- Low power design for HW implementation

- Minimum HW cost in ASIC implementation

- Flexible HW architecture

-

NR-5G Polar Encoder /Decoder

- The NR-5G Polar encoder/decoder is developed for 5G new radio.

- Fully compliant with 3GPP TS 38.212 Sections 5.2.1, 5.3.1, 5.4.1 and 5.5

-

NR-5G Polar Decoder and Encoder

- The Forward Error Correction (FEC) sub-system is one of the essential basing blocks in any communication systems so a powerful FEC code is needed.

- The New Radio (NR) FEC for the control channel is proposed to be designed based on Polar codes allowing close to the Shannon limit/Capacity operation.

- The Polar code successive cancellation decoding process as needed for 3GPP physical layer standard.

-

100 Gbit/s Polar Encoder and Decoder with soft-decision LLR input

- Fully synchronous design, using single clock

- Fully synthesizable drop-in module for FPGAs

- Optimized for high performance and low resources

-

Generic Polar FEC Encoder and Decoder

- Fully-pipelined architecture

- Support for systematic and non-systematic encoding

- Support for coded block lengths of up to 1024 bits

- Support for a wide variety of

-

5G Polar encoder/decoder

- CRC handling, with scrambling mask, configurable LFSR init.

- Interleaver for distributed CRC