eFPGA – Hidden Engine of Tomorrow’s High-Frequency Trading Systems

By Menta

What are the modern challenges facing designers of high-frequency trading systems?

High-frequency trading (HFT) system designers face challenges that go far beyond raw speed. Today, it’s about squeezing out nanoseconds while managing ever-growing complexity, security risks, and regulatory pressures. Every picosecond matters – profitability is directly tied to latency, with firms pushing closer to the physical limits of the speed of light.

At the same time, algorithms must remain adaptable to evolving exchange protocols and shifting compliance rules. Discrete FPGAs have provided flexibility, but they bring their own challenges in performance, power, and integration. ASICs promise higher speed and efficiency, yet their rigidity leaves designers with an almost impossible trade-off.

The way forward is clear: ASICs coupled with adaptable hardware, such as Menta embedded FPGA (eFPGA). This hybrid approach delivers the raw performance of ASICs while preserving the flexibility needed to adapt in real time—a practical answer to what has long seemed like a Sisyphean task.

Let’s examine the modern challenges facing HFT designers—and why Menta eFPGA is uniquely positioned to solve them.

| Problem Category | Challenge | Details |

| Latency | Performance of current systems | Tightly coupling processing hardware with high-speed transceivers to reduce the compute envelope |

| Determinism | Predictable processing solutions | Trade-off between ASIC (fast), FPGA/eFPGA (adaptable), and software (flexible but slow) |

| Data & Analytics | Processing of real-time data streams | Terabytes of market data daily; bandwidth/memory bottlenecks; NUMA/cache management critical |

| Power/Thermal | Heat & Energy efficiency + constraints of modern rack systems | Dense servers, accelerators, liquid/immersion cooling; latency penalties from throttling. Systems need to operate within constraints of current systems |

| Security | In-line, hardware-base packet processing security with crypto agility | Side-channel/fault-injection risks; secure boot, obfuscation, PQC adoption |

| Verification | Debugging at nanosecond scale | Difficult to validate correctness; deterministic replay & timestamping required |

| Regulation | Compliance overhead | MiFID II/SEC logging, order traceability, latency equalization, speed bumps |

| Future-proofing | AI deployment and acceleration; Post-quantum readiness | PQC is compute-heavy; integrating AI/ML for inference at nanosecond scales still unsolved |

How does adaptable hardware benefit HFT ASICs?

In a nutshell, ASIC speed coupled with FPGA flexibility equals ultra-latency, performance and most importantly, adaptability. Let’s break down aspects of HFT architectures and discuss how eFPGA benefit each of these.

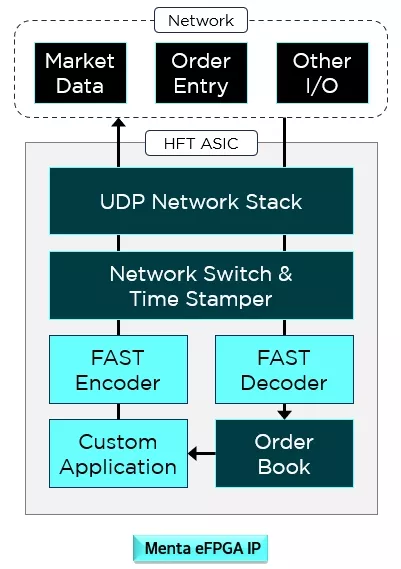

Figure 1: Typical HFT Architecture

Market Data Handler

Market data handlers (MDH) are the first critical step in the HFT pipeline, responsible for normalizing, filtering, and enriching tens of millions of messages per second from multiple venues. These feeds arrive in diverse formats, with exchange protocols frequently updated or modified, and require nanosecond-resolution timestamping for compliance and auditability. Designers must normalize, filter, and enrich this firehose of data in sub-microsecond timeframes.

This is where Menta eFPGA technology comes in. With on-the-fly reconfiguration, eFPGA parsing engines adapt instantly to new feed formats—eliminating the risk of ASIC obsolescence and avoiding costly, time-consuming redesigns. Menta’s eFPGA, built entirely from standard foundry cells, allows designers to tune for performance or power while remaining independent of commercial FPGA technology nodes. You get the freedom to deploy on faster, lower-power process nodes of your choice.

That adaptability doesn’t just solve today’s problems—it future-proofs your MDH architecture for AI-driven enhancements, novel security features, and whatever tomorrow’s markets throw at you.

Signal Engine

The signal engine is the heartbeat of any HFT stack, where raw market data is transformed into actionable signals within nanoseconds. This demands ultra-low-latency (ULL) decision making, where even minor jitter can turn a profitable trade into a loss. When you combine the complexity of statistical models, order book dynamics, and real-time risk constraints, only adaptable hardware can keep pace.

Menta’s eFPGA delivers exactly that. With on-the-fly reconfigurability, the fabric can be updated in microseconds to reflect evolving strategies or risk rules. Its inherent parallelism and pipelining allow multiple signals to be processed concurrently—ideal for multi-venue correlation and cross-asset strategies. By tightly coupling the eFPGA to the data path, serialization delays are eliminated, ensuring the highest possible performance.

Beyond today’s speed demands, this architecture also future-proofs signal engines. Emerging AI/ML inference kernels can be mapped directly into the fabric for ultra-fast pattern recognition, while advanced crypto-agility features—such as obfuscation and rolling keys—secure proprietary signal logic against attack.

Risk & Compliance Checks

Risk and compliance checks must operate inline with the trading pipeline, enforcing position limits, credit thresholds, and regulatory safeguards without adding overhead. Regulators demand nanosecond-precision timestamping and complete traceability, all while markets and compliance rules evolve frequently. Software implementations cannot meet these latency requirements, and ASICs lack flexibility for regulatory change. With Menta eFPGA, deterministic enforcement of risk rules can be performed at nanosecond speeds, while new thresholds, models, or compliance checks can be deployed dynamically—avoiding downtime or costly respins. Parallel enforcement of multiple risk parameters ensures scalability, and crypto-agility features secure both audit logs and proprietary compliance logic. By embedding these capabilities directly into the data path, eFPGA guarantees speed, adaptability, and auditability in one architecture.

Execution & Order Management

At the final stage, execution and order management systems must handle order placement, acknowledgments, modifications, and cancellations across multiple venues with deterministic, ultra-low latency. Every nanosecond impacts execution quality and profitability. Traditional software introduces jitter, while fixed ASICs cannot keep up with rapidly changing exchange protocols and new order types. Menta eFPGA provides a unique solution by embedding adaptable execution logic directly into the ASIC, ensuring consistent nanosecond-level performance with the ability to reprogram routing policies, order types, or venue-specific protocol handlers in real time. This integration minimizes serialization delays, reduces system complexity, and positions trading firms to adapt seamlessly to future market structure changes, regulatory shifts, or novel execution mechanisms.

Monitoring & Telemetry

In high-frequency trading, what you don’t see can hurt you. Monitoring and telemetry provide visibility into system performance, latency distribution, order flow behavior, and compliance alignment. Firms must capture nanosecond-accurate timestamps across the pipeline and generate audit trails that satisfy strict regulatory standards such as SEC Rule 613 (CAT) or MiFID II. At the same time, telemetry must be non-intrusive—it cannot add measurable latency or distort the very signals it observes.

Software-based telemetry introduces unacceptable overhead, while fixed ASIC logic lacks the flexibility to evolve with new monitoring requirements. By embedding Menta eFPGA into the infrastructure, firms can implement deterministic, hardware-level timestamping and event capture at wire speed, without impacting performance. eFPGA fabric can be reprogrammed to support new monitoring rules, extended counters, or real-time anomaly detection. Beyond compliance, this enables performance optimization, including identifying microbursts, correlating multi-venue order flow, and detecting nanosecond-level jitter. Looking forward, eFPGA provides the foundation for AI-based monitoring and predictive diagnostics, ensuring transparency and resiliency as trading infrastructure grows more complex.

Conclusion

Across the HFT pipeline—from market data handling to signal generation, risk enforcement, execution, and monitoring—the common requirement is deterministic ultra-low latency coupled with adaptability. Software is flexible but too slow, ASICs are fast but rigid, and discrete FPGAs introduce integration, power, and vendor-dependency challenges. By embedding Menta eFPGA fabric directly into ASICs, this adaptable hardware delivers the speed of custom silicon with the flexibility of reconfigurable hardware, future-proofing HFT infrastructure against the evolving demands of markets, regulators, and technology itself.

Menta’s soft eFPGA IP completely configurable to meet your specific HFT requirements, based on 100% standard cell libraries and is uniquely:

- Foundry-independent – implementable on any process

- Fast to deploy – delivered in RTL in just days

- Cost-efficient – reduced NRE and downstream cost

- Flexible and secure – obfuscated bitstream unique to each device

- Production ready – highest yield, best testability

- Proven – silicon validated across foundries, with radiation-hardened options

- Customizable – supports 3rd party block RAMs, patented DSPs

About Menta

Menta, a pioneering leader in embedded FPGA (eFPGA) technology with over 15 years of proven success, delivers 100% standard-cell, third-party embedded FPGA IP for SoC, ASIC, and ASSP designs. As the only pure-play eFPGA provider offering silicon-proven, synthesis-free IP, Menta empowers semiconductor designers to adapt post-production — enabling rapid updates for bug fixes, customer-specific customizations, evolving standards, or enhanced security.

Our cutting-edge IP is delivered with the Origami toolchain, a seamless solution that generates bitstreams directly from RTL, streamlining design and accelerating time-to-market. Trusted by global semiconductor leaders, Menta transforms chips into agile, future-proof platforms — redefining what’s possible in silicon design. Want to learn more? Contact us at info@menta-efpga.com

Related Semiconductor IP

- eFPGA Soft IP

- eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- eFPGA on GlobalFoundries GF12LP

- eFPGA Hard IP Generator

Related Articles

- Redefining Speed: How FPGAs are shaping the future of high-frequency trading

- Android, Linux and Real-Time Development for Embedded Systems

- NAND Flash memory in embedded systems

- eFPGA Creator GUI Tools Suite: A complete hardware and software infrastructure for creating customizable eFPGA IP blocks of Menta

Latest Articles

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks