An Open-Source Approach to Developing a RISC-V Chip with XiangShan and Mulan PSL v2

By Jonah McLeod, RISC-V Industry Analyst

February 13, 2025

As RISC-V gains traction in the global semiconductor industry, developers are exploring fully open-source approaches to processor design. XiangShan, a high-performance RISC-V CPU project, combined with the Mulan Permissive License v2 (Mulan PSL v2), represents a community-driven, transparent alternative to proprietary chip development models. Unlike traditional IP licensing models, where companies purchase pre-configured processor cores, XiangShan allows full access to RTL (register-transfer level) source code, enabling deep hardware customization. With the support of MinJie, an agile open-source development platform, and UnityChip, an open-source verification framework, XiangShan provides a flexible and scalable development path for startups, research institutions, and semiconductor companies looking to build custom RISC-V chips.

This article explores the design process of developing a RISC-V chip using XiangShan, highlighting the advantages, challenges, and impact of an open-source development approach.

Key Design Elements of the Chip

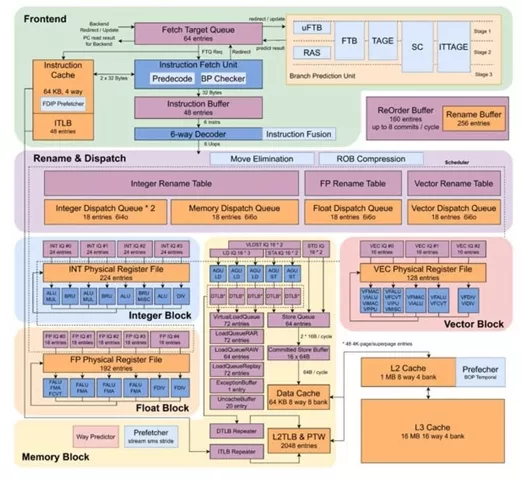

The latest generation of XiangShan, known as Kunminghu (Gen3), is designed to deliver high-performance computing capabilities, making it a viable alternative to commercial RISC-V processors. It features out-of-order execution with a high-performance pipeline, support for RISC-V vector extension for AI and HPC acceleration, and scalability for different process nodes, including 7nm, 12nm, and 28nm fabrication.

To streamline the design and development process, XiangShan utilizes MinJie, an open-source development platform that integrates Chisel-based RTL development, simulation and performance profiling tools, and agile methodologies, reducing iteration time for hardware design. One of the biggest challenges in open-source hardware is ensuring reliability and security. UnityChip provides functional verification to detect architectural bugs early, security verification to test speculative execution vulnerabilities (such as Spectre-like attacks), and crowdsourced debugging tools, enabling contributions from universities and independent researchers. Together, these elements form a comprehensive, open-source RISC-V development ecosystem, fostering innovation while maintaining full transparency.

Chisel (Constructing Hardware in a Scala Embedded Language) is a high-level hardware description language (HDL) that simplifies register-transfer level (RTL) design by enabling more modular, reusable, and parameterized hardware development compared to traditional HDLs like Verilog and VHDL.

In Chisel-based RTL development, designers use Scala-based programming constructs to define digital circuits, allowing for faster prototyping, better code reusability, and easier debugging. It integrates with simulation and performance profiling tools, which help validate design correctness, optimize computational efficiency, and analyze power consumption. These tools enable pre-silicon verification, ensuring that a processor meets performance targets before fabrication.

For RISC-V processor development, Chisel-based tools streamline core design, integration of vector extension, and instruction scheduling, making them particularly useful for projects like XiangShan, which require high customization and an agile development cycle.

Development Process and Challenges

The development of a custom RISC-V chip using XiangShan and Mulan PSL v2 follows a structured but highly customizable approach. Developers begin by selecting and customizing the processor core. They start with Kunminghu (Gen3), choosing features such as vector extension and cache configurations. Since the RTL is fully open-source, modifications can be made at a deep architectural level. Unlike proprietary IP cores, developers have complete control over performance tuning, instruction scheduling, and power efficiency.

Once the processor core is selected, RTL design and simulation take place using MinJie, which provides a modular, Chisel-based design flow that enables rapid prototyping. The high-level hardware description language allows flexible modifications while maintaining efficiency. Developers conduct pre-silicon simulations, optimizing logic before physical design.

Verification and testing are performed using UnityChip, which integrates multiple verification methodologies to ensure robust functionality. Security analysis is conducted to prevent speculative execution attacks and cache vulnerabilities. The verification framework also enables collaborative debugging, allowing research institutions and independent developers to contribute to improving the design.

The final step in the process is fabrication. XiangShan cores are designed to be scalable across multiple process nodes, including 7nm, 12nm, and 28nm. Developers can choose local or international fabs such as TSMC, SMIC, or GlobalFoundries based on cost and geopolitical considerations. The Mulan PSL v2 license ensures that there are no commercial restrictions, making it easier to integrate into commercial silicon products.

Table. XiangShan Versus Proprietary Commercial RISC-V IP

| Aspect | XiangShan (Mulan PSL v2) | Proprietary RISC-V IP (Commercial Vendors) |

| Licensing | Fully open-source | Requires paid IP license |

| Customization | Full RTL access, high flexibility | Limited customization, pre-configured cores |

| Development Tools | MinJie (open-source agile development) | Proprietary toolchains |

| Verification | UnityChip (community-driven verification) | Vendor-provided, closed testing |

| Security Testing | Open security analysis | Limited transparency |

| Manufacturing Freedom | Fabrication at any foundry | Some IPs are restricted to certain fabs |

| Cost | Free (no licensing fees) | License fees required |

The Open-Source Advantage: Why Choose XiangShan?

XiangShan provides a unique advantage over proprietary RISC-V IP by offering full RTL access and high flexibility, unlike commercial vendors that limit customization through pre-configured cores. Development tools such as MinJie enable agile, open-source development, while proprietary solutions rely on vendor-specific toolchains. Verification is performed through UnityChip, a community-driven framework that encourages open security analysis, whereas commercial IP vendors provide proprietary closed testing. Another key advantage is that XiangShan allows fabrication at any foundry, whereas some proprietary IP solutions may have restrictions on manufacturing partners. With no licensing fees, XiangShan provides a cost-effective alternative, making it ideal for academic research, AI startups, and semiconductor companies looking to fully control their chip design.

Conclusion: The Future of Open-Source RISC-V Chips

The combination of XiangShan, Mulan PSL v2, MinJie, and UnityChip provides a complete, open-source alternative to proprietary RISC-V development. This approach is highly customizable, giving developers full control over their chip’s architecture and performance. It is also cost-effective, eliminating licensing fees and enabling broader adoption in academic and startup environments. Additionally, it is scalable and secure, integrating advanced verification tools to ensure reliability and security.

With continuous community contributions and growing industry adoption, XiangShan is positioned as a leading open-source RISC-V project, pushing the boundaries of open innovation in semiconductor design.

Jonah McLeod, RISC-V Industry Analyst jonah@jonahmcleod.com

Related Semiconductor IP

- All-In-One RISC-V NPU

- ISO26262 ASIL-B/D Compliant 32-bit RISC-V Core

- RISC-V CPU IP

- Data Movement Engine - Best in class multi-core high-performance AI-enabled RISC-V Automotive CPU for ADAS, AVs and SDVs

- Low Power RISCV CPU IP

Related White Papers

- A guide to accelerating applications with just-right RISC-V custom instructions

- A comprehensive approach to enhancing IoT Security with Artificial Intelligence

- BCD Technology: A Unified Approach to Analog, Digital, and Power Design

- New Realities Demand a New Approach to System Verification and Validation

Latest White Papers

- Transition Fixes in 3nm Multi-Voltage SoC Design

- CXL Topology-Aware and Expander-Driven Prefetching: Unlocking SSD Performance

- Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

- Automating NoC Design to Tackle Rising SoC Complexity

- Memory Prefetching Evaluation of Scientific Applications on a Modern HPC Arm-Based Processor