Adaptable Hardware with Unlimited Flexibility for ASIC & SoC ICs

By Menta

For over 40 years, FPGA technology has driven the advancement of emerging technologies. However, the high cost, size, and power requirements of traditional FPGAs have confined their use to low-volume applications. Over 15 years ago, Menta pioneered embedded FPGA (eFPGA) technology, democratizing FPGA capabilities and enabling any ASIC or SoC manufacturer to seamlessly integrate this IP into their devices. This technology has empowered a wider range of applications to benefit from the flexibility and performance advantages of FPGA technology.

Embedding FPGAs offers endless possibilities. Firstly, as technology becomes increasingly complex and volatile, adding adaptable hardware can mitigate risks for critical components and algorithms. This allows them to be completed or fixed even after the integrated circuit has been taped out. This approach also accelerates the tape-out process and gets products to market faster, which can be a key factor in a product’s success. Furthermore, adaptability enables designers to create a single device that can serve multiple markets and applications, namely those with ITAR restrictions that have diverse security, compression, interface, and feature requirements.

FPGA architectures offer a natural advantage for accelerating complex, highly parallel algorithms with the benefits of pipelined processing. This makes them particularly well-suited for emerging and novel algorithms that do not run efficiently or deterministically on traditional processors. Additionally, this enables low latency for applications that require compact compute windows for real-time response. Applications like cryptography, image/video processing, motor control, and AI inferencing can all leverage the power of FPGAs.

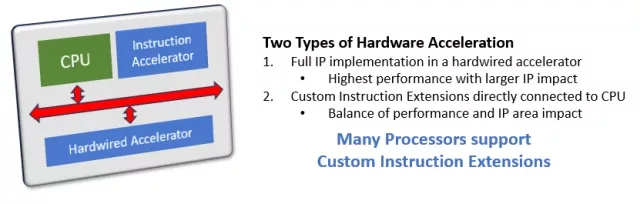

Our innovative solutions can isolate complex functions and accelerate them as custom instructions extended from a processor like RISC-V. These optimized instructions can be implemented in a tiny eFPGA area, dramatically reducing cost, power, and chip size. With Menta’s flexible soft IP offering, you can easily tune this IP to perfectly match the needs of your specific algorithms.

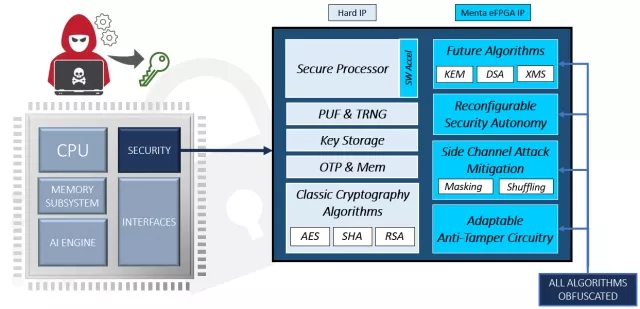

Furthermore, critical data processing can be made more robust by implementing redundant processing and isolating data/memory from CPU systems. By programming algorithms only in secure environments, the IP can be effectively obfuscated, preventing theft through invasive chip deconstruction and reverse engineering tactics.

This combination of acceleration, robustness, and security makes FPGAs a compelling solution for a wide range of complex, high-performance, and high-volume applications.

There are only a few eFPGA suppliers on the market today, and Menta is the sole provider of a completely flexible IP offering based 100% on standard cells. This means Menta’s eFPGA IP can be utilized on any technology node and tuned to meet your exact performance and power requirements. Our cutting-edge technology offers exceptional versatility, enabling seamless integration into rad-hard cells for mission-critical applications in the medical, automotive, and industrial sectors, including demanding space environments.

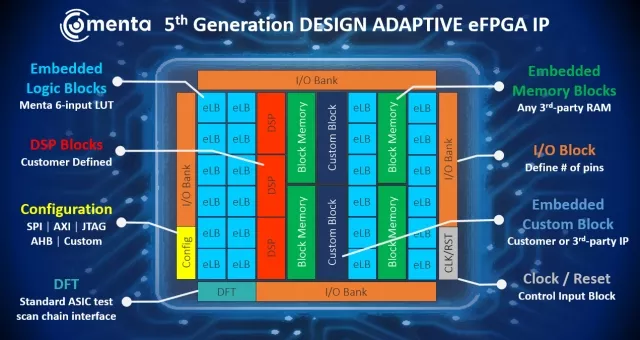

Menta’s eFPGA IP is the most advanced on the market, featuring a highly optimized 6-input look-up table architecture. As a soft IP offering, Menta’s solution gives customers complete flexibility to choose the exact logic, memory, and digital signal processing resources they need and not be bound by restrictions of fixed hard IP offerings of eFPGA.

Menta’s architects work closely with designers to provide the optimal eFPGA solution, which can be delivered to customers in a matter of weeks, not months as with hard IP solutions. This unparalleled flexibility and rapid turnaround time make Menta the premier choice for embedded FPGA technology.

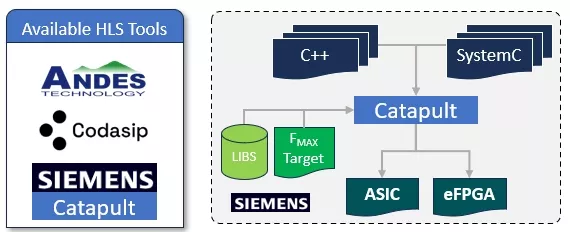

Menta works closely with an ecosystem of partners to accelerate IP integration. These partners can help with design implementation as well as software IP solutions optimized for Menta’s IP and architecture. For example, Trusted Semiconductor Solutions specializes in rad-hard implementations and has assisted several customers with integrating Menta’s eFPGA IP. IMEC is highly specialized in nanotechnology and digital integration. Siemens, Andes Tech, and Codasip have proven RISC-V solutions with examples of processor instruction acceleration using Menta’s eFPGA IP.

Additionally, IP partners like Synopsys, SecureIC, Qualcomm/Tiempo, and PQSecure provide RTL optimized for Menta’s eFPGA architecture to provide robust, long-lasting security solutions by enabling crypto agility, obfuscation, and side-channel attack mitigation.

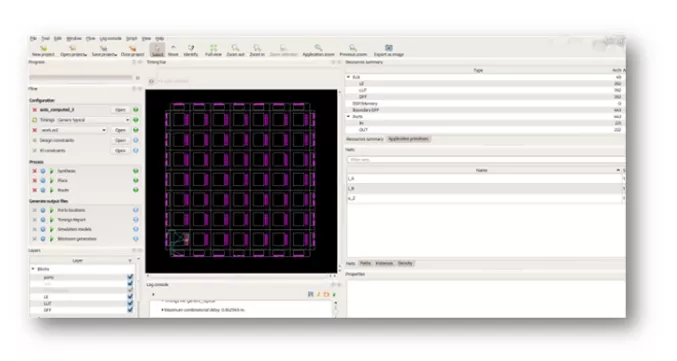

Menta provides a full EDA tool suite for our eFPGA IP. Origami Programmer is a state-of-the-art, robust and easy-to-use programming software to synthesis, place & route, run STA, and generate the bitstream that targets/optimizes the users’ RTL specifically to its Menta eFPGA architecture. With full EDA tool ownership, customers have the ability to redistribute these tools as well as integrate them into their own tools.

Menta’s configuration memory offers unparalleled advantages over SRAM-based eFPGA solutions. Firstly, it is the only configuration memory based purely on standard library D flip-flops, providing inherently high reliability tied to the technology node library. This enables exceptional test coverage, currently exceeding 99.7% stuck-at and 95% at-speed – massive benefits that save customers significant time and money during test.

Seeking flexibility and adaptability? Menta’s eFPGA IP solution can be 100% customized to your exact needs, saving you time and money while helping you differentiate your products and get them to market quickly. Break free from rigid IP constraints if hard IP and let Menta’s tailored approach empower your innovation.

About Menta

Menta, a privately held company, provides 100% third-party standard-cell embedded FPGA intellectual property (IP) for system-on-chip (SoC), application-specific integrated circuit (ASIC), and application-specific standard product (ASSP) designs. Our innovative technology allows users to easily update silicon post-production, whether to fix a bug, implement customer-specific features, adapt to evolving standards, or enhance security. Menta’s IPs are delivered with the Origami toolchain, which generates the bitstream directly from the register transfer level (RTL), including synthesis.

Related Semiconductor IP

- eFPGA Soft IP

- eFPGA

- eFPGA on GlobalFoundries GF12LP

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- Radiation-Hardened eFPGA

Related White Papers

- Accelerating SoC Evolution With NoC Innovations Using NoC Tiling for AI and Machine Learning

- A RISC-V Multicore and GPU SoC Platform with a Qualifiable Software Stack for Safety Critical Systems

- Nine Compelling Reasons Why Menta eFPGA Is Essential for Achieving True Crypto Agility in Your ASIC or SoC

- Add Security And Supply Chain Trust To Your ASIC Or SoC With eFPGAs

Latest White Papers

- Ramping Up Open-Source RISC-V Cores: Assessing the Energy Efficiency of Superscalar, Out-of-Order Execution

- Transition Fixes in 3nm Multi-Voltage SoC Design

- CXL Topology-Aware and Expander-Driven Prefetching: Unlocking SSD Performance

- Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

- Automating NoC Design to Tackle Rising SoC Complexity