System Level Solutions's eUSB 3.1 Gen2 Device Controller (eUSB31SF) IP core now available with Isochronous transfer support

September 9, 2021 -- For 16 years, SLS has been providing USB IP core solutions. After many successful deliveries for various high-speed data transfer applications, SLS has now launched an eUSB 3.1 Gen2 Device Controller (eUSB31SF) IP core with Isochronous transfer type support. This added feature further enhances applications in the Audio, Video, Multimedia, Broadcast, Streaming, Space Communication, and Telecommunication sectors for transfer time-sensitive information.

Benefits with Isochronous Transfers

- Guaranteed access to USB bandwidth.

- Bounded latency.

- Stream Pipe - Unidirectional

- Error detection via CRC

- No data toggling improving speed

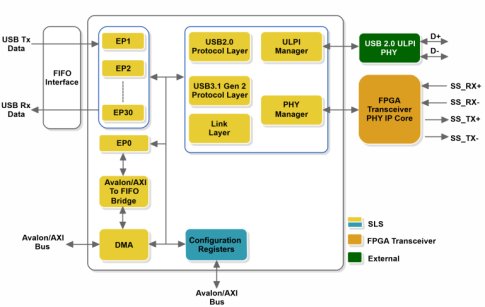

In addition to supporting Control and Bulk endpoints, the eUSB31SF IP core supports High-speed, High bandwidth Interrupt and Isochronous transfers.

eUSB31SF IP core Key Features:

- Supports Control, Bulk, Interrupt and Isochronous transfers

- Supports SSP (USB 3.1 Gen 2), SS (USB 3.1 Gen 1), FS (12 Mbps) and HS (480 Mbps) modes

- Uses FPGA’s Transceiver as a PHY layer

- Eliminates need for external PHY for USB 3.1 mode

- Reduces IO pin usage

- Reduces BOM cost

- Eliminates need for external PHY for USB 3.1 mode

- Capable to support simultaneous IN requests to different endpoints in SSP mode

- Capable to support up to 31 endpoints (1 default control endpoint +15 IN/OUT endpoints)

- Software configurable endpoints

- Ready to use component

- Simple FIFO interface to transfer data over non-control endpoint

- Allows user to select number of buffers per endpoint based on the requirement

For quick prototype and reduced design cycles, SLS provides the IP core along with add-ons such as a time limited License for encrypted IP core, Reference design, Demonstration, Software tools, Technical documents and Support. SLS provides pre and post-sales technical support for generating programming files and validating the System design.

“With the Isochronous support added to the eUSB 3.1 Gen2 Device Controller IP core applications requiring Guaranteed Bandwidth and Bounded Latency are easily realized in FPGA based products ” emphasizes - CEO SLS Pvt ltd.

With quality processes in places through ISO 9001:2015 and ISO 14001:2015 certification as well as qualified engineers, System-Level Solutions, an integration specialist, provides innovative solutions spanning intellectual property, hardware, software design, and manufacturing. For any query related to eUSB 3.1 Gen2 Device Controller (eUSB31SF) IP core, please visit our website www.slscorp.com or write us at info@slscorp.com

Related Semiconductor IP

- USB 3.1 Cable Marker IP

- USB 3.1 PHY

- USB 3.1 Host Premium

- USB 3.1 DRD Premium

- SuperSpeed USB 3.1 Host Controller Multiport

Related News

- Webinar : USB 3.1 Gen2 Device Controller IP Core usage in Intel Quartus Prime Pro

- CAST Introduces Microsecond Channel Controller IP Core for Automotive Power and Sensor Interfaces

- DI3CM-HCI, A High-Performance MIPI I3C Host Controller IP Core for Next-Generation Embedded Designs

- Digital Blocks DB9000 Display Controller IP Core Family Extends Leadership in 8K, Automotive, Medical, Aerospace, and Industrial SoC Designs

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard