OmniPHY Unveils 25G Backplane SerDes Silicon on TSMC 28nm Technology

Low-latency architecture paves the way for mass adoption of 100GbE Ethernet

San Jose, Calif. – March 30, 2017 – OmniPHY Inc. today announced silicon availability of its industry-leading, low-latency backplane SerDes PHY which delivers enterprise-class performance in demanding backplane applications. Developed on TSMC’s 28nm process technology based on relevant IEEE 802.3 standards, this solution meets the growing demands of data center applications, while also minimizing latency for emerging applications like financial transaction processing.

“To meet the growing demand for low-latency high-speed Ethernet, we have developed a high-performance design on a mainstream process node,” said Claude Gauthier, Chief Technology Officer of OmniPHY. “Additionally, the design is truly multi-protocol and capable of supporting several protocols from 1- to 28Gb/s. It is great to see the silicon validate our rigorous design methodologies.”

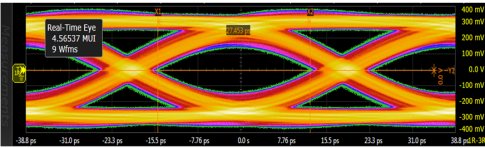

Figure 1: Transmitted 25G Eye Diagram

The industry-standard interfaces offered by OmniPHY are robust and designed to operate under harsh electrical conditions. For additional information on OmniPHY products and solutions, or to schedule a technology demonstration, please contact sales@omniphysemi.com.

About OmniPhy

Omniphy is an American mixed-signal semiconductor IP company based in San Jose, California, with satellite offices across the world. The company specializes in intellectual property and develops high-performance Ethernet PHYs and SerDes interfaces for the Automotive, Industrial, Consumer, and Networking markets. For more information visit http://omniphysemi.com or contact sales@omniphysemi.com.

Related Semiconductor IP

- 25G PHY, TSMC N6 x2 North/South (vertical) poly orientation

- 25G PHY, TSMC 7FF x4 North/South (vertical) poly orientation

- 25G PHY, TSMC 7FF x2 North/South (vertical) poly orientation

- 25G PHY, TSMC 7FF x1 North/South (vertical) poly orientation

- 25G PHY, TSMC 16FFPGL x4 North/South (vertical) poly orientation

Related News

- PLDA and OmniPhy Announce PCIe Gen 2 Controller and PHY Combination for the TSMC 28nm Process

- OmniPhy Announces 2.5v I/O Transistor based Mixed Signal PHY Availability in TSMC 28nm HPM

- Faraday Leads Industry with 28G Programmable SerDes at 28nm for Networking ASIC

- MosChip Announces Multi-Protocol Long Range 8G SerDes PHY in 28nm

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard