Defacto Technologies Automates Front-End SoC Integration for Large RISC-V Designs

Grenoble, France – April 11, 2025 – Defacto Technologies, a key player in EDA solutions for SoC design, announces the update of its SoC Compiler software to automate front-end SoC integration flows for complex RISC-V architectures. This innovation is designed to address the growing complexity and scalability challenges of RISC-V SoC designs. The new Defacto’s SoC Compiler Release will be presented at the RISCV Summit in Paris, France, from May 12 to 15, 2025.

The open-source RISC-V architecture is increasingly used across embedded applications such as mobile, IoT, computing, and beyond. While RISC-V offers flexibility and openness, the RTL design process for RISC-V SoCs is created and optimized using internal solutions (through custom scripts) and remains largely manual particularly for multicore processors and large-scale architectures.

Three Major Limitations of Current RISC-V Design Practices

Despite internal scripting and tools, current front-end integration processes face structural inefficiencies.

Lack of Design Reusability

Designs are typically built for specific configurations and lack portability across projects.

Building a complex SoC design project typically involves several key steps: selecting and configuring IPs, interconnecting them, generating the necessary design files for implementation and verification flows, and completing the validation phase. This entire process is repeated for each new project.

This results in time loss and inefficiency as teams must recreate design integration from scratch.

Manual and Iterative Processes

From IP selection and configuration to connection and file generation, the process remains predominantly manual. Iterating over large RISC-V SoCs is time-consuming and error-prone.

Fragmented IP Management

For the same IP core, managing the gap between internal and updated open source IPs is a painful process. Differences between open-source RISC-V IPs (e.g. GitHub-based) and customized internal versions require attention and continuous updates.

Modifications to one affect modifications to the other, and teams waste time and energy coordinating all together.

A New Era of Automation with Defacto’s SoC Compiler

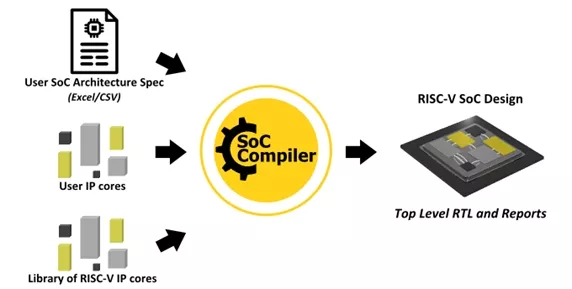

To overcome these challenges, Defacto’s SoC Compiler allows users to quickly explore and generate different SoC configurations — from RTL to design collaterals — based on user specifications, with minimal manual parametrization and intervention.

Our new software includes, in-depth RTL linting checks by covering VHDL, Verilog and System Verilog languages. Also structural checks such as connectivity, clock tree and interfaces checks etc.

The Defacto software delivers a comprehensive set of features designed to optimize SoC integration pre synthesis. It includes an optimized and up-to-date library of configurable RISC-V IP cores, along with the ability for users to integrate their own custom IPs.

Using Python or Tcl APIs, Designers can leverage a variety of SoC design templates to accelerate development, while built-in checking capabilities ensure quality through linting checks for IP cores and coherency checks between multiple design views. The tool is fully compatible all RTL languages Verilog, VHDL, and SystemVerilog, and offers extensive customization options to adapt to diverse project requirements.

In addition, the RTL restructuring features such as Feedthrough management enable designers to optimize Power, Performance, and Area (PPA). They help adapt the design to fit with physical requirements by refining structures such as removing long loops, loopbacks, and redundant ports. These enhancements support aggressive die size reduction and significantly improve the reusability of designs and IPs across projects.

The tool also facilitates the integration of design changes, speeding up the iteration process and optimizing coordination between teams.

Tangible Benefits

With Defacto’s SoC Compiler, RISC-V design configuration is simplified and faster than manual methods. Engineering teams can efficiently generate and manage RISC-V-based SoC designs, resulting in faster design cycles and reduced turnaround time. They can dedicate more attention to debugging, optimizations, and high-value design tasks, while also benefiting from improved reusability of IPs and architectures across projects.

This approach aligns with the growing demand for scalable and automated design methodologies as RISC-V continues to expand its footprint in high-performance embedded applications.

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- MIPI Alliance Updates its MIPI RFFE Interface for Mobile Device RF Front-End Architectures

- Defacto enables ETRI to Automate IP Integration and Build Complex AI Chips

- Arteris Celebrates 3rd Year of Automotive ISO 26262 TCL1 Functional Safety Compliance for Magillem SoC Integration Automation

- S2C and Andes Technology Announce FPGA-Based Prototyping Partnership to Accelerate Advanced RISC-V SoC Development

Latest News

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud

- Analog Bits Demonstrates Real-Time On-Chip Power Sensing and Delivery on TSMC N2P Process at TSMC 2026 Technology Symposiums

- TES offers a High-Frequency Synthesizer and Clock Generator IP for X-FAB XT018 - 0.18µm BCD-on-SOI technology

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware