Ashling Announces RiscFree™ Debug and Trace Support for Tenstorrent TT-Ascalon™ RISC-V CPUs

Silicon Valley, CA – August 21, 2025 – Ashling today announced full debug and trace support for Tenstorrent’s Ascalon RISC-V CPU within its RiscFree SDK.

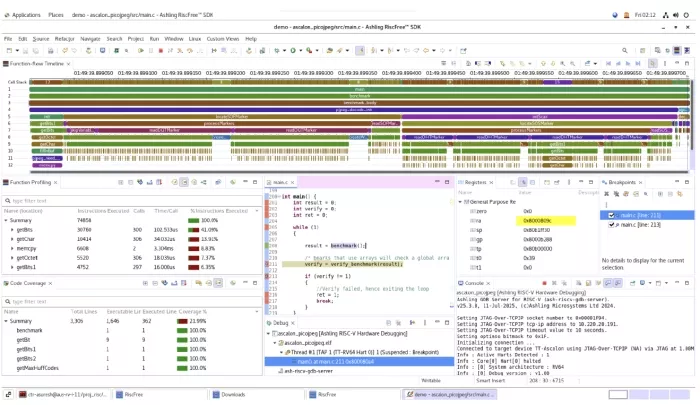

RiscFree provides comprehensive visibility and control across the entire software stack—from low-level drivers to high-level application code. With features including breakpoints, step/continue execution, register and memory inspection, real-time trace, and multi-core support (both homogeneous and heterogeneous), RiscFree enables efficient debugging, tracing and performance tuning of complex embedded systems. This collaboration ensures that developers targeting Tenstorrent’s high-performance Ascalon RISC-V cores can now rely on a robust and proven tool chain to accelerate development, debugging, and system validation.

Figure 1: Ashling’s RiscFree debugging and tracing on Tenstorrent’s Ascalon RISC-V core.

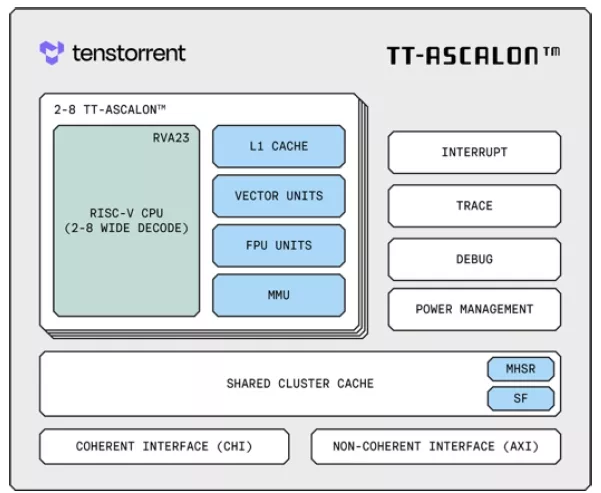

Figure 2: Tenstorrent’s Ascalon RISC-V core.

TT-Ascalon is Tenstorrent’s high-performance RISC-V CPU, built on open standards to provide maximum flexibility and architectural control. It is based on the open RISC-V ISA and is RVA23 compliant. With support for two to eight cores per cluster and a configurable shared L2 cache, Ascalon is designed to scale across a wide range of applications. Ascalon also supports CHI.E and AXI5-LITE interfaces and incorporates a TrustZone-equivalent security model built on RISC-V primitives, it delivers high performance density while maintaining an open, vendor-neutral foundation.

A central focus of the Ashling–Tenstorrent collaboration is comprehensive trace support, built on the RISC-V standard N-Trace architecture. RiscFree integrates with Tenstorrent’s Ascalon CPUs to capture detailed trace data across multi-core systems, enabling real-time visibility into instruction execution, memory transactions, and key system events.

“Trace is critical for understanding software behaviour on complex SoCs, especially when debugging subtle timing or interaction issues,” said Hugh O’Keeffe, CEO of Ashling. “By supporting standardised RISC-V N-Trace, we ensure that developers can rely on open, interoperable tooling for trace capture and analysis.”

In addition to N-Trace, Tenstorrent’s Debug Signal Trace (DST) infrastructure has been fully implemented in its Ascalon CPUs, providing access to critical micro-architectural signals alongside standard trace data during post-silicon validation. DST enhances debugging, performance analysis, and coverage, and is fully supported by Ashling’s RiscFree tools—enabling deep trace visibility with minimal integration overhead.

“DST is now fully integrated into the Ascalon platform, and with its support in tools like RiscFree, the RISC-V ecosystem is now empowered to seamlessly adopt DST in their IP implementations,” said Sajosh Janarthanam, Lead Engineer at Tenstorrent. “By standardising access to low-level trace signals, we’re reducing debug complexity and improving the overall RISC-V development experience. Our contribution of an open Debug Signal Trace specification to the community reflects Tenstorrent’s commitment to open-source innovation—lowering integration costs and enabling more capable and accessible debug and trace solutions across the RISC-V ecosystem.”

About Tenstorrent

Tenstorrent is a next-generation computing company that builds computers for AI. Tenstorrent is headquartered in North America and has locations in Toronto, Austin, Boston, and Silicon Valley, and global offices in Belgrade, Tokyo, Bangalore, and Seoul, Tenstorrent brings together experts in the field of computer architecture, ASIC design, advanced systems, and neural network compilers. Tenstorrent is backed by Eclipse Ventures and Real Ventures, among others. Learn more at www.tenstorrent.com.

About Ashling

Ashling is a world leader in the development of tools and solutions for embedded systems and the semiconductor industry. With a focus on enabling software design for next-generation processors and SoCs, Ashling offers cutting-edge debugging tools, trace probes, and development environments. https://www.ashling.com/contact-ashling/ email:info@ashling.com.

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- Ashling Microsystems Announces New High Performance Debug and Trace Probe for ARM devices

- Tenstorrent Productizes RISC-V CPU And AI IP

- Quintauris and Lauterbach Elevate RISC-V Debug & Trace Capabilities for Automotive

- Ashling and Imagination announce Ashling's RiscFree™ C/C++ SDK support for RISC-V-based Catapult family

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud