Akeana tapes out highest performance RVA23 Alpine test chip

4nm silicon/software development board includes 64b Server class Out-of-order cores, 64b/32b Control/Vector In-order cores with SMT, System IP, LPDDR5, PCIe5

January 22, 2026 -- The tape out of Alpine in December 2025 was a major milestone – for Akeana and more broadly for the RISC-V ecosystem that is craving RVA23 compatible high-performance silicon for software development. Working closely with our SoC development partner, we taped out the highest performance RVA23 compatible Server class SoC. Alpine, as we will describe below, helps connect the value proposition dots for Akeana, and delivers a world class software development vehicle.

Background

Alpine was introduced at the RISC-V summit in October 2025. Akeana has developed a unique customizable RISC-V IP platform that spans the performance spectrum from low end to high end cores. This flexible approach is critical to extract the maximum value from an open extensible RISC-V ISA. It is also the efficiency multiplier for Akeana, whereby a small startup can bring to market a full portfolio of cores spanning the ARM roadmap. Alpine showcases the power of this approach and has IP that spans the Akeana product portfolio. A unique flexible design platform also requires complementary verification methodology and systems. Akeana has developed a 24×7 verification solution that has run trillions of verification cycles across multiple configurations of the Akeana IP portfolio. It is this robust approach to quality IP that enables rapid customization and instance level verification for specific tape outs such as Alpine. Alpine showcases the unique RISC-V design and verification technology platform created by Akeana, and the on-schedule tape out demonstrates the execution strength of the company, that is built around a team that has worked together for decades.

Alpine was introduced at the RISC-V summit in October 2025. Akeana has developed a unique customizable RISC-V IP platform that spans the performance spectrum from low end to high end cores. This flexible approach is critical to extract the maximum value from an open extensible RISC-V ISA. It is also the efficiency multiplier for Akeana, whereby a small startup can bring to market a full portfolio of cores spanning the ARM roadmap. Alpine showcases the power of this approach and has IP that spans the Akeana product portfolio. A unique flexible design platform also requires complementary verification methodology and systems. Akeana has developed a 24×7 verification solution that has run trillions of verification cycles across multiple configurations of the Akeana IP portfolio. It is this robust approach to quality IP that enables rapid customization and instance level verification for specific tape outs such as Alpine. Alpine showcases the unique RISC-V design and verification technology platform created by Akeana, and the on-schedule tape out demonstrates the execution strength of the company, that is built around a team that has worked together for decades.

RISC-V is emerging as an AI native heterogeneous hardware-software co-design platform, and this is what Akeana is enabling for our customers. Akeana’s platform enables single ISA scalar, vector, matrix computation and can integrate with other accelerator engines. It leverages a unified software stack including compilers and toolchains for the hardware platform. We had described this holistic approach in our AI solutions webinar, and also how our unique SMT capabilities are serving heterogeneous compute applications. Alpine encompasses the key building blocks that are required to realize this platform.

Alpine

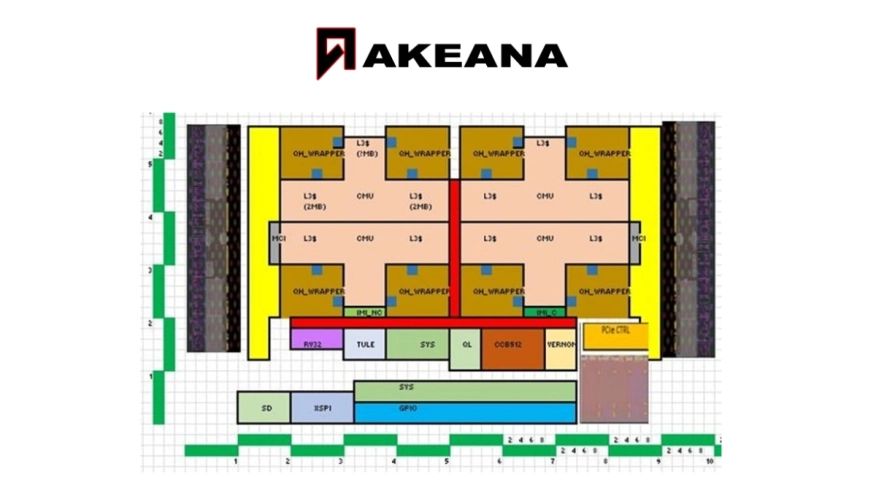

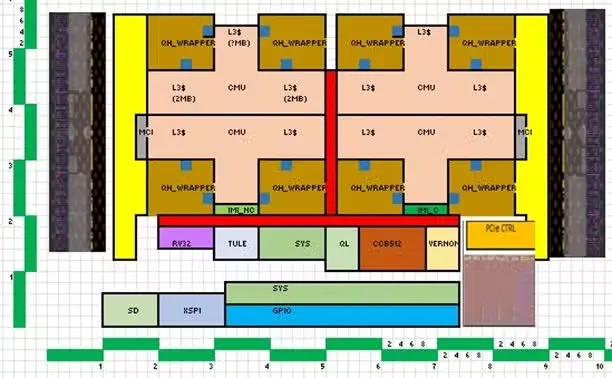

- The floorplan below reflects the Alpine test chip. It is comprised of the following key Akeana IP:

- Eight 64b out-of-order core cluster in a coherent mesh. The cores are the entry level offering from our 5000 series. A 2×2 CHI mesh, each with 2 cores in a coherent block form the 8-core cluster. Each core has L1/L2 cache of 64 KB/256 KB with a shared 4 MB L3 cache per 2 core cluster. Each core has a 2x128b vector engine. These are Neoverse class application processors cores, RVA23 compatible for easy Linux integration and also meet the Server SoC specification. The use cases for this core include CPU-xPU systems, data center applications such as SmartNICs, Storage and Memory accelerators, Automotive ADAS chips, and wearable SoCs.

- 64b in-order core, 4-way simultaneous multi-threaded, 512b vector engine with support for a variety of math formats. The use cases for this core include AI control and vector processing, data movement engines, as well as data plane processing applications.

- 32b in-order core. The use cases for this core include system management, security processor, and real-time applications.

- System IP includes a non-coherent AXI bus to integrate the compute and IO subsystems, and RISC-V compliant IOMMU, AIA interrupt controllers.

Key IO IP from third party partners have also been integrated into Alpine. These include two LPDDR5 channels and x4 PCIe Gen5. Alpine will be made available on a software development board (SDB) with memory, storage options, as well as a range of network and device connectivity options enabled with an on-board PCIe switch and also include BMC functionality. To enable easy SDB bring up, Akeana has pre-verified Alpine on our extensive emulation platforms with Linux OS running prior to tape out.

Explore RISC-V IP

SDB Availability and Reservation

Alpine SDBs will be made available to potential customers and partners starting in the second half of 2026. We are currently taking reservations so please contact sales@akeana.com to express interest including highlighting quantity desired, target applications, and any specifics on software porting/development work that you intend to do.

In addition, if there is interest in partnering on future test chips with different Akeana IP configurations, higher performance cores, and/or foundry/process choices, please reach out to sales@akeana.com to express interest.

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- RIVAI Launched China’s First Fully Self-Developed High- Performance RISC-V Server Chip

- S2C and Andes Technology Announce FPGA-Based Prototyping Partnership to Accelerate Advanced RISC-V SoC Development

- Andes and Arculus System Collaborate to Integrate iPROfiler™ into AndeSysC, Expanding Virtual Platform Support for RISC-V SoC Design

- Arteris and Alibaba DAMO Academy Extend Partnership to Accelerate High-Performance RISC-V SoC Designs

Latest News

- Alchip Appoints Freddy Engineer Chief Business Officer and North America General Manager

- Perceptia Devices and Dolphin Semiconductor Partner to Deliver Best-in-Class IP Portfolio Covering Power Management, Clocking, High-Quality Audio and In-Situ Monitoring

- TSMC Chases Soaring AI Demand

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems