VCXO IP

Filter

Compare

13

IP

from

7

vendors

(1

-

10)

-

ISDB-S3 demodulator

- The CMS0071 ISDB-S3 Demodulator is a high-performance (A)PSK demodulator core intended for ARIB STD-B44 ISDB-S3 advanced wide band digital satellite standard.

- Operating symbol rate is programmed from a register and extends from approximately 40% of the master clock frequency down to an arbitrary low rate that is set through synthesis options. The range would normally be dictated by the application and, in particular, the phase noise characteristics of the radio system.

-

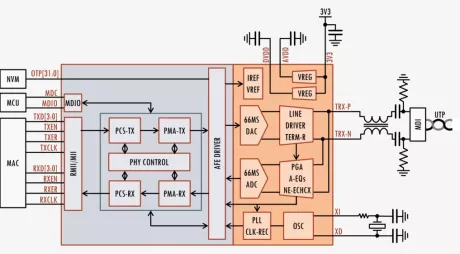

100BASE-T1 (OABR) Ethernet PHY IEEE 802.3bw Compliant

- OABR V3.2 Compliant

- IEEE 802.3bw Compliant

- IEEE 1588 PTP Support under design

-

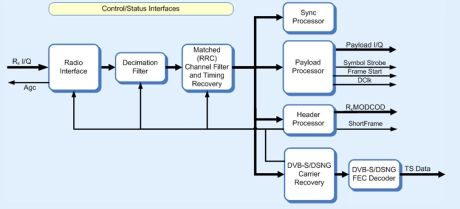

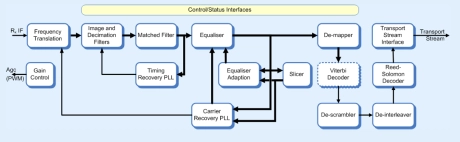

DVB-S demodulator / DSNG demodulator

- The CMS0048 DVB-S/DSNG Demodulator is a high-performance (A)PSK demodulator core intended for DVB-S and DVB DSNG forward link applications.

- The demodulator provides soft-constellation outputs together with recovered QAM information suitable for decoding by the integrated DVB-S/DSNG FEC decoder. The TS output stream is smoothed before being output from the core.

-

DVB-Satellite demodulator

- The CMS0059 Satellite Demodulator is a high-performance (A)PSK demodulator core intended for DVB-S, DVB-DSNG, DVB-S2 and DVB S2X forward link applications.

- The DVB-S and DVB-DSNG “plug-in”s provide soft constellation outputs together with recovered QAM information suitable for decoding by the integrated DVB-S/DSNG FEC decoder. The recovered TS output stream is smoothed before being output from the core.

-

Serdes 32:1 for 8.5-11.3Gb/s for SONET/SDH, 10GbE, XFI, Back Plain

- Data-rates from 8.5Gb/s to 11.3Gb/s.

- High sensitivity input (15mV SE p-p)

- Adjustable input signal equalizer

- Clock and Data Recovery

-

Serializer 32:1 for 8.5-11.3Gb/s for SONET/SDH, 10Ge, XFI, Back Plain

- Data-rates from 8.5Gb/s to 11.3Gb/s.

- Digital 32-bit input

- Output CML 50Ω terminated

- Output swing 400mV or 250mV p-p SE

-

DVB-C demodulator / J83 demodulator

- The CMS0022 DVB-C/J.83 Cable Demodulator is a 4th generation design that exploits the vendor’s experience of QAM and OFDM systems for broadband terrestrial, satellite and cable modems.

- The core forms an integrated cable demodulator solution comprising of the Universal QAM Demodulator(CMS0006) and J.83abc/DVB-C Cable FEC Decoder(CMS0018) cores.

-

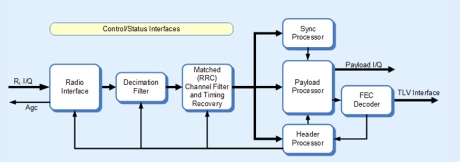

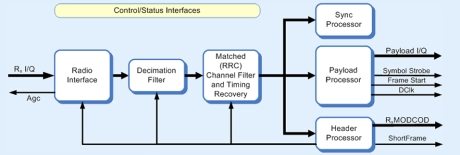

DVB-S2 (A)PSK Demodulator

- The CMS0014 DVB-S2 (A)PSK Demodulator is a high-performance (A)PSK demodulator core intended for DVB-S2 and DVB-S2X forward link applications.

- The demodulator is compatible with the ACM, VCM and CCM configurations of the DVB-S2 Standard including DVB-S2 extensions and is therefore suitable for the reception of DVB broadcast, DSNG, professional and broadband interactive services.

-

SMIC 0.13um 1.2~3.3V Voltage Controlled Crystal Oscillator

- Process: SMIC 0.13um 1.2/3.3v 1P6M/7M/8M CMOS logic process

- Supply voltage: 1.08V~1.2V~1.32V; 3.0V~3.3V~3.6V

- Current: TBD

- Operating temperature: - 40°C ~ +25°C ~ +125°C

-

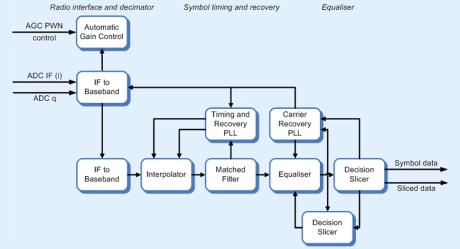

Multi-mode QAM Demodulator

- IF sub-sampling or I/Q baseband interface.

- Variable ADC width support.

- Single external clock source required.

- Single external analogue loop for AGC.