UHD 4K IP

Filter

Compare

43

IP

from

12

vendors

(1

-

10)

-

4K Video Scaler IP Core

- Technology independent soft IP Core for FPGA, SoC and ASIC devices

- Supplied as human readable VHDL source code (or Verilog on request)

- Versatile RGB video scaler capable of scaling up or down by any factor

- Fully programmable scale parameters and scaler bypass function

-

UHD Serial Digital Interface (UHD-SDI)

- SMPTE ST 259: SD-SDI at 270 Mb/s

- SMPTE RP 165: EDH for SD-SDI

- SMPTE ST 292: HD-SDI at 1.485 Gb/s and 1.485/1.001 Gb/s

- SMPTE ST 372: Dual Link HD-SDI (by instantiation of two UHD-SDI cores)

-

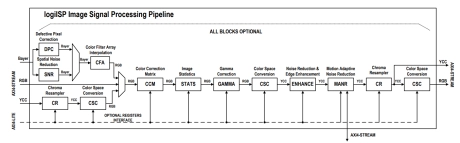

UHD Image Signal Processing (ISP) Pipeline

- The logiISP-UHD Image Signal Processing Pipeline IP core is an Ultra High Definition (UHD) ISP pipeline designed for digital processing and image quality enhancements of an input video stream in Smarter Vision embedded designs based on Xilinx ACAP, MPSoC, SoC and FPGA devices.

- It enables parallel processing of multiple Ultra HD video inputs in different programmable devices, ranging from the small Xilinx Artix®-7 FPGAs to the latest Xilinx Versal Adaptive Compute Acceleration Platform (ACAP) devices.

-

-

-

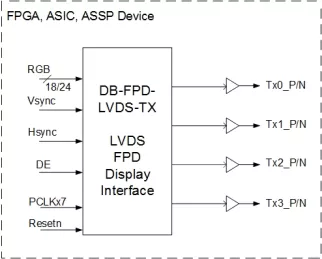

FPD LVDS Display Interface, 1 Port / 2 Port LCD Panel

- The DB-FPD-LVDS-TX LVDS Display Interface IP Core interfaces parallel 18-bit/24-bit RGB Pixel Data with display timing VSYNC, HSYNC, Data Enable, and Pixel Clock to a FPD LVDS compliant display panel via 3 or 4 or 5 LVDS Differential Data Pairs and 1 LVDS Differential Clock Pair.

-

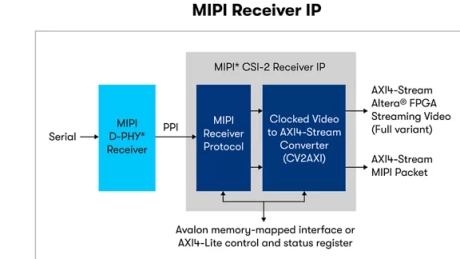

MIPI D-PHY IP

- Mobile Industry Processor Interface (MIPI) D-PHY is supported on Agilex™ 5 and Agilex™ 3 FPGAs allowing transmission and reception of data through PHY-protocol interface (PPI) to connect with camera serial interface (CSI) and display serial interface (DSI) applications.

-

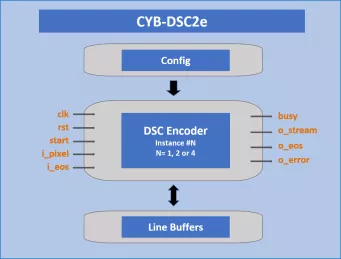

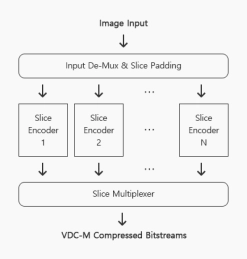

VDC-M 1.2 Encoder

- VESA Display Compression-M (VDC-M) 1.2 Compliant

- 8, 10, or 12 bits per Color Support

- 4:4:4 RGB Native Encoding

- 4:4:4, 4:2:2, or 4:2:0 YCbCr Native Encoding

-

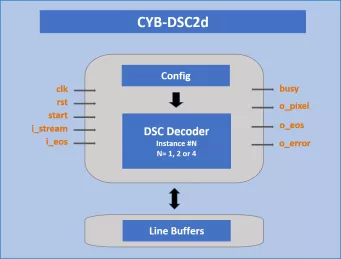

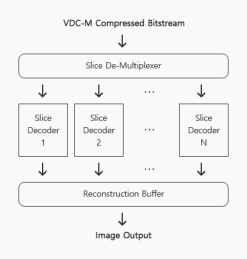

VDC-M 1.2 Decoder

- VESA Display Compression-M (VDC-M) 1.2 Compliant

- Ultra-low Latency

- Reduces Power and System Costs

- Slice Configuration : 1, 2, 3, 4

- Optimized for Power Saving

-

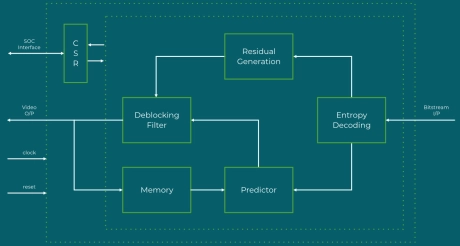

H.265 Decoder

- The H.265 (HEVC – High Efficiency Video Coding) Decoder IP core delivers high-performance video decompression for next-generation visual applications, including broadcast, surveillance, automotive, and consumer electronics.

- It supports real-time decoding of ultra-high-definition (UHD) video streams, up to 4K and 8K resolutions, while significantly reducing bandwidth and storage requirements without compromising video quality.