UFS MIPI IP

Filter

Compare

81

IP

from

9

vendors

(1

-

10)

-

MIPI UFS v3.1 Host Controller IP, Compatible with M-PHY and Unipro

- Compliant with the JEDEC UFS v3.1

- Backward compatibility JEDEC UFS v3.0 & v2.1

- TAG overlap/LBA overlap/Valid UPIU check

- Maximum DATA OUT = 64KB

-

MIPI UFS v2.1 Host Controller IP, Compatible with M-PHY and Unipro

- Compliant with UFS Specification v2.1 and backward compatible t

- AXI support

- All UPIU processing

- Data-in, data-out, command, response, RTT, query, task management and reject

-

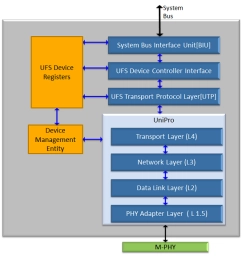

MIPI UFS v3.1 Device Controller IP, Compatible with M-PHY and Unipro

- Compliant with UFS Specification v3.1 and backward compatible to UFS v3.0 & v2.1

- AXI support

- All UPIU processing

- Data-in, data-out, command, response, RTT, query, task management and reject

-

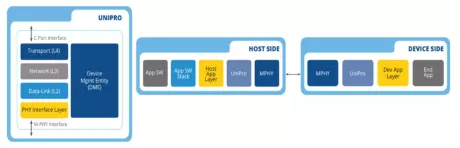

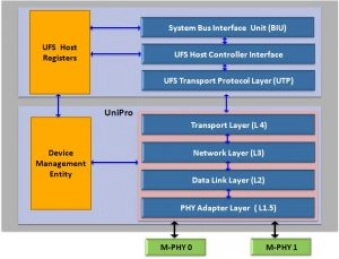

MIPI Unipro v1.6 Controller IP, Compatible with M-PHY and UFS

- Compliant with MIPI UniPro Standard V1.6 and MPHY standard 3.x

- Programmable 1, 2, or 4 data lanes

- Support for M-PHY HS data rates HS-Gear-1, Gear-2, Gear-3, both A/B modes and PWM data rates PWM-G1 to PWM-G7

- Support for end-to-end flow control

-

MIPI Unipro v1.8 Controller IP, Compatible with M-PHY and UFS

- Compliant with the MIPI UniPro v1.8 specification and backward compatible with MIPI UniPro v1.61

- Support HS-Gear4 M-PHY IP v4.1 and access to attribute

- Support Asymmetric lanes and Gears

- Support Data Lanes connected 2 lanes

-

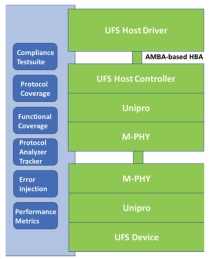

Verification IP for UFS

- Avery UFS/Unipro VIP provides a comprehensive verification solution featuring an advanced UVM environment that incorporates: constrained random SCSI and Unipro traffic generation, robust packet and physical layer controls and error injection, protocol checks and coverage, functional coverage, protocol analyzer-like features for debugging, and performance analysis metrics.

-

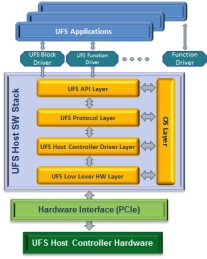

UFS 2.1 Stack & Driver

- Compliant with JEDEC UFS HCI 2.0 and MIPI UniPro Specification version 1.6

- Portability in choice of OS, processors and hardware

- Easy-to-use interface for applications

- Fully documented generic device operation API

-

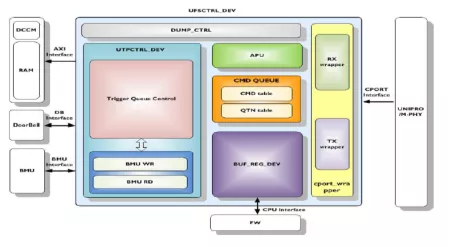

UFS 2.1 Device Controller IP

- The UFS 2.1 Device controller uses an M-PHY® 3.1 Adapter Layer backed by a UniPro v1.6 Link layer controller as per the specification.

- The UFS compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms.

-

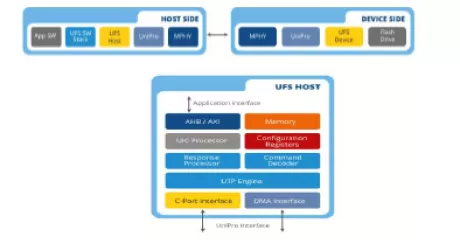

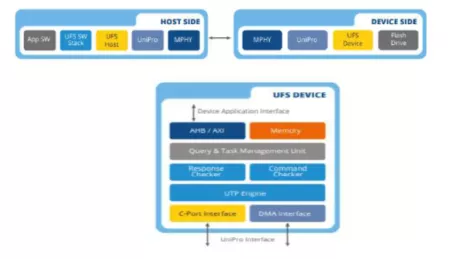

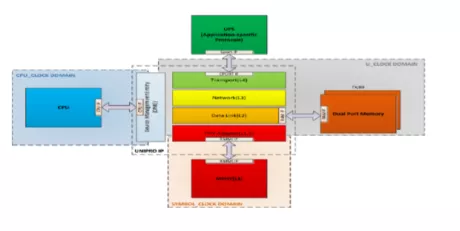

UFS 3.0 Host

- UFS 3.0 Host and Device configurations available

- Complete UFS 3.0 hardware implementation

- Interop-proven UniPro 1.8 link layer

- MIPI M-PHY 4.0 Interface

-

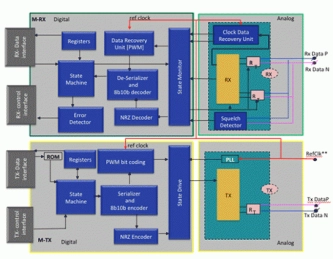

MIPI M-PHY® 3.1 Analog Transceiver

- The M-PHYs are of Type 1, which apply to UFS, LLI and CSI-3 protocols.

- The Multi-gear M-PHY 3.0 consists of analog transceivers, high speed PLL, data recovery units as well as the state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant to the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.