SpRAM generator IP

Filter

Compare

27

IP

from

14

vendors

(1

-

10)

-

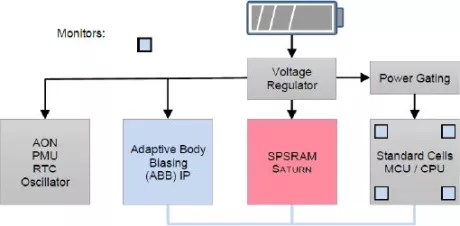

Low Power Memory Compiler - Single Port SRAM - GF 22nm FDX

- Silicon proven Single Port SRAM compiler for GF22 FDX - Memory optimized for low power and supports body biasing.

-

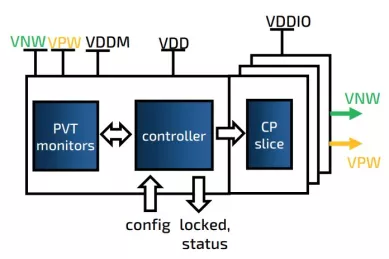

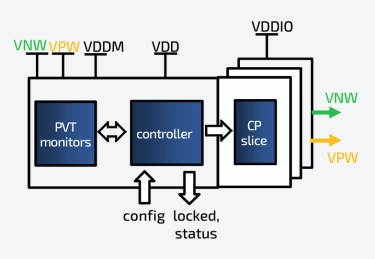

Automotive Adaptive Body Biasing Generator - GLOBALFOUNDRIES 22FDX

- RI_ABB_GF22FDX_AM is an adaptive body bias voltage generator for automotive applications in Globalfoundries 22FDX® technology.

- It contains a closed loop body bias regulation loop to generate N-well and P-well bias voltages for compensation of process, voltage and temperature (PVT) variations during operation.

- This results in up to 76% leakage power improvement for automotive grade-1 applications up to 150°C junction temperature.

-

Single Port SRAM compiler - Memory optimized for ultra high density and high speed - compiler range up to 64 k

- Smart periphery design to reach the highest density

- Memory designed with SVT MOS for periphery and SVT HD PRBC from TSMC for memory core

- Flexible architecture

- To offer several performance trade-offs for any memory size

-

Adaptive Body Bias Generator - GLOBALFOUNDRIES 22FDX

- RI_ABB_GF22FDX is a cutting-edge adaptive body bias (ABB) generator for GLOBALFOUNDRIES® 22FDX® technology.

- Featuring patented closed control loops with independent N-well and P-well body bias voltage generation, this silicon-proven IP dynamically compensates for process, voltage, and temperature (PVT) variations during operation.

-

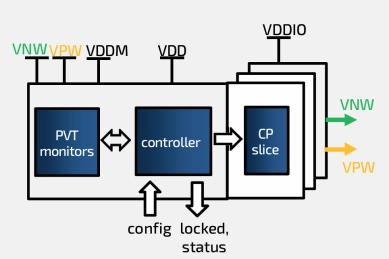

Adaptive Body Biasing Generator - GLOBALFOUNDRIES 22FDX

- RI_ABB_GF22FDX is a cutting-edge adaptive body bias (ABB) generator for GLOBALFOUNDRIES® 22FDX® technology.

- Featuring patented closed control loops with independent N-well and P-well body bias voltage generation, this silicon-proven IP dynamically compensates for process, voltage, and temperature (PVT) variations during operation.

-

Single Port SRAM compiler - Memory optimized for high density and low power - compiler range up to 320 k

- Memory generator

- SVT TSMC Bit-cell for memory core and SVT MOS for memory periphery

- Migration of a mass produced architecture already available in other geometries(90nm, 55 nm)

- Up to 30% denser than competition SRAM

-

Single Port SRAM compiler - Memory optimized for high density and low power - compiler range up to 320 k

- Foundry sponsored memory generator

- Configuration

- uLL TSMC Bit-cell for memory core and uLL MOS for memory periphery

- Migration of an existing architecture already available for other processes (90, 85, 55 nm)

-

Single Port SRAM compiler - Memory optimized for ultra high density and low power - compiler range up to 576 k

- Configuration

- SVT transistors for memory periphery

- HD HVT Pushed rule bit cell from foundry

- Smart periphery design

-

Single Port SRAM compiler - Memory optimized for ultra high density and high speed - compiler up to 64 k

- Foundry sponsored memory generator

- Smart periphery design to reach the highest density

- Memory designed with SVT MOS for periphery and SVT HD PRBC from TSMC for memory core

- Flexible architecture

-

TSMC CLN12FFC 500MHz Analog Front-End

- TSMC 12 nm 0.8 V/1.8 V CMOS LOGIC FinFET Compact Process

- Metal scheme: 1P9M (2Xa1Xd_h_3Xe_vhv_2Z) + UT-ALRDL

- Operating junction temperature: -40 °C ~ 125 °C

- 2-ch 12 bit 250 MHz SAR ADC