Silicon Creations IP

Filter

Compare

7

IP

from

1

vendors

(1

-

7)

-

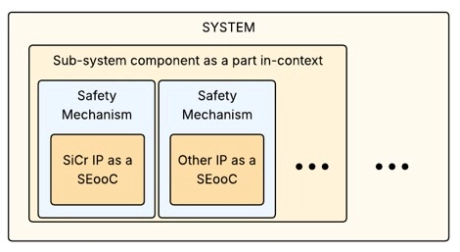

Automotive Grade PLLs, Oscillators, SerDes PMAs, LVDS/CML IP

- TSMC IP9000 Alliance member enabling automotive IP support in TSMC automotive processes

- Automotive Documentation including Safety Manual, FMEDA and DFMEA

- Design reliability report containing EM/IR and Aging analysis

-

General-purpose & Specialized Ring PLLs + RTL-based Solutions

- Wide functional range allows all frequencies in a system to be synthesized with one PLL macro

- Input & output frequency ranges greater than 1000:1

-

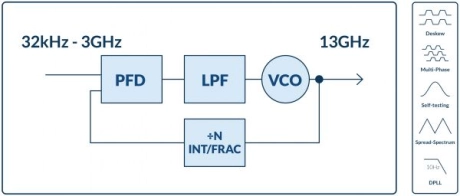

High Quality LC-PLLs

- Automatically locks over an extremely wide input frequency range

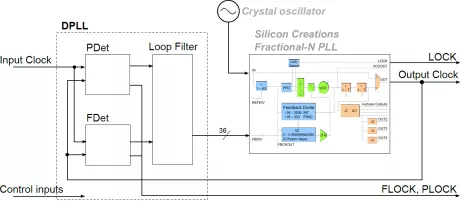

- Dual-loop P

- Wideband integrated jitter <400fs in integer mode, <800fs in fractional mode with high-speed / clean reference with active fractional noise cancellation

- Passes PCIe6 reference clock requirements with wide margin

- Reference spur <200fs RMS

- Random period jitter <30fs RMS

- LL effective loop bandwidth can be arbitrarily small

-

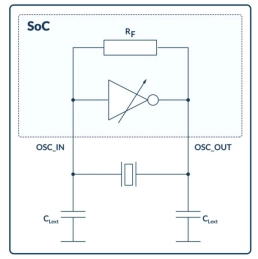

Crystal Oscillators

- The crystal oscillator macros are available in a wide range of industry-standard quartz crystals and MEMS resonators operating in the fundamental mode in the 32 kHz to 80 MHz range.

- These oscillators, which are both power and area efficient, have a programmable transconductance to allow users to find the optimal balance between jitter and power consumption.

-

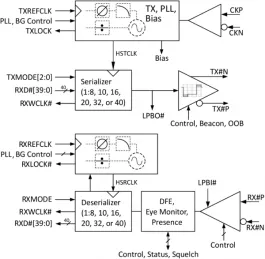

Multiprotocol SerDes PMA

- Supports over 30 protocols including CEI 6G & 11G SR, MR, LR, Ethernet 10GBASE-X/S/K/R, PCIe Gen1/2/3/4, V-by-One HS/US, CPRI, PON, OTN/OTU, 3GSDI, JESD204A/B/C, SATA1-3, XAUI, SGMII

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, or 40 bit

- Tx ring PLL includes fractional multiplication, spread spectrum and Jitter Cleaner function for Sync-E and OTU

- Core-voltage line driver with programmable pre-and post-emphasis

-

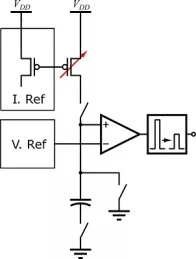

Free running oscillators

- Compact and low power

- No external components

- Baseline CMOS logic process masks only

- Excellent frequency precision over PVT after trimming

-

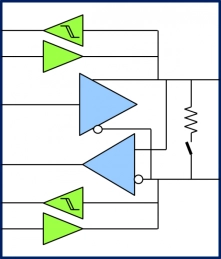

LVDS interfaces

- Wide operating range

- High data rates

- Very flexible programmability

- Excellent signal integrity

- TIA/EIA644A LVDS and sub-LVDS compatibility

- Receiver also compatible with LVPECL