Serial ATA IP

Filter

Compare

79

IP

from

14

vendors

(1

-

10)

-

Dual Serial ATA 1.5/3.0/6.0 Gbps Phy

- Serial ATA fully compliant to Gen 1,Gen 2 and Gen3 SATA Phy Standards.

- Transmit and receive data at 1.5Gbps, 3.0 Gbps and 6.0 Gbps.

- High-speed differential reference clock

- Low jitter clock synthesizers for clock distribution

-

Serial ATA I/II/III Host Controller IP Core Compliance Certified by UNH Labs

- High Throughput

- Low Latency

- Connects to SAPIS compliant serial ATA Phy

-

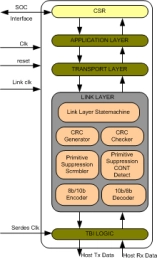

Serial ATA Dual Host Controller

- Physical Layer features

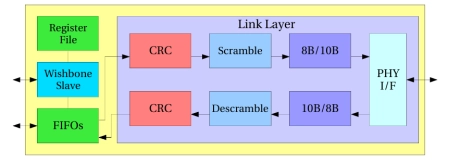

- Link Layer features

- Transport Layer features

-

Serial ATA I/II Device Controller IP Core

- The Serial ATA Device Controller IP Core provides an interface to high-speed serial link replacements for the parallel ATA attachment of mass storage devices.

- The serial link employed is a high-speed differential layer that utilizes Gigabit technology and 8b/10b encoding.

-

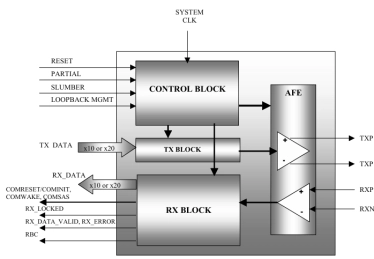

Serial ATA (SATA) PHY Transceiver IP

- SMS6000 is a fully integrated CMOS transceiver that handles the low level Serial ATA protocol and signaling.

- It contains all necessary Clock synthesis, Clock Recovery, Serializer, Deserializer, Comma detect for 8B/10B encoded data and Frame alignment functionalities.

-

Dual Parallel to Serial ATA 1.5/3.0Gb/s PHY Core

- Serial ATA fully compliant to Gen 1 and Gen 2 SATA PHY Standard.

- Single and Dual data rate capable of transmit and receive at 1.5Gb/s and 3.0 Gb/s.

- High-speed differential reference clock

- Low jitter clock synthesizers for clock distribution

-

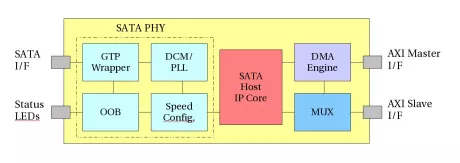

SATA HOST CONTROLLER IIP

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

-

SAS INITIATOR IIP

- Supports SPL 1.0/2.0/3.0/4.0/5.0 Specs

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

-

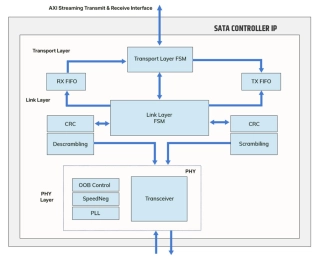

SATA 3 Controller IP

- Simple AXI streaming TX and RX interface for application layer communication.

- It supports Native Command Queuing and key primitives/FIS types from SATA specifications.

- Compliant with Serial ATA 3.0 specification.

- Supports data rates of 1.5/3/6 Gbit/s.

-

SATA 6G PHY in GF (40nm, 28nm)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection