SPAUI IP

Filter

Compare

73

IP

from

31

vendors

(1

-

10)

-

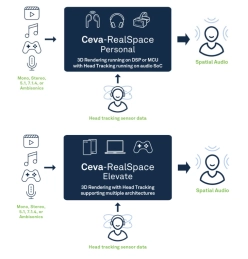

Spatial Audio & Head Tracking Solution

- Ceva-RealSpace is a complete Spatial Audio software solution combining precise 3D rendering and accurate, low-latency head tracking.

- RealSpace supports multiple system architectures, giving you the flexibility to render content directly on TWS earbuds, headphones, XR headsets, or speakers for the lowest latency. Or choose to render on mobile phones, gaming systems, or PCs and save BOM costs on the device.

- RealSpace operates independently of audio codec choices, source vendors, or device ecosystems. Pre-integrated on some of the top audio SoCs in the industry, Ceva-RealSpace helps you bring cutting-edge products to market faster and with less risk.

-

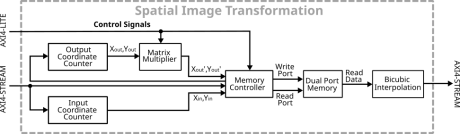

Spatial image transformation accelerator

- Streaming is compatible with AXI-Stream protocol

- Transformation and image dimension parameters are configurable through AXI4-Lite

-

Analog I/O Library with a custom 12V ESD Solution IN GF 55nm

- This I/O library is a silicon-proven, flip-chip-optimized analog and mixed-signal I/O Library for GlobalFoundries 55nm BCD technology.

- It provides a comprehensive set of 1.8V, 3.3V, 5V, and 12V analog I/O and power pads, designed for robust ESD protection, flexible pad-ring construction, and reliable operation across industrial temperature ranges.

-

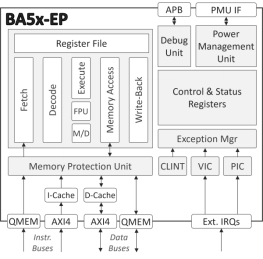

Enhanced-Processing Embedded RISC-V Processor

- The BA5x-EP is a highly-featured 32-bit RISC-V embedded processor IP core optimized for complex, processing-demanding applications.

- It is equipped with a floating-point unit and cache memories, supports hardware-level virtualization, and is suitable for concurrent execution in a multi-processor environment.

-

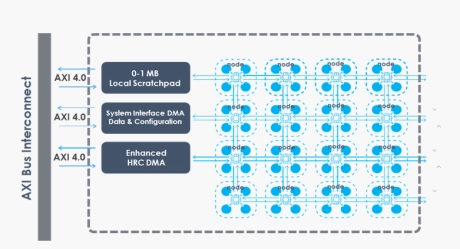

Dataflow AI Processor IP

- Revolutionary dataflow architecture optimized for AI workloads with spatial compute arrays, intelligent memory hierarchies, and runtime reconfigurable elements

-

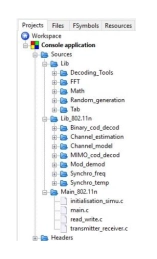

802.11ax PHY Layer C Floating-Point Code IP for the STA mode

- This IP includes a recommendation-compliant 802.11ax PHY layer C floating-point code for the Station (STA) mode.

- The code is integrated into a simulation environment that allows the configuration of mandatory features and the performance evaluation in terms of frame error rate.

- It is designed to generate fixed-point sequences in order to accelerate the development of both C fixed-point code and HDL code for prototyping environments.

-

Neuromorphic Processor IP (Second Generation)

- Supports 8-, 4-, and 1-bit weights and activations

- Programmable Activation Functions

- Skip Connections

- Support for Spatio-Temporal and Temporal Event-Based Neural Network

-

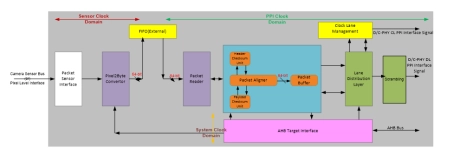

CSI-2 v2.1 Transmitter IP

-

Arasan IP Core that functions as a MIPI CSI-2 Transmitter, which typically resides in a mobile platform’s camera module, and communicates over a D-PHY/C-PHY link to a CSI2 Receiver in the applications processor.

-

The Arasan CSI-2 combo IP is MIPI-compliant and provides a standard, scalable, low-power, high-speed interface that supports a wide range of higher image resolutions.

-

-

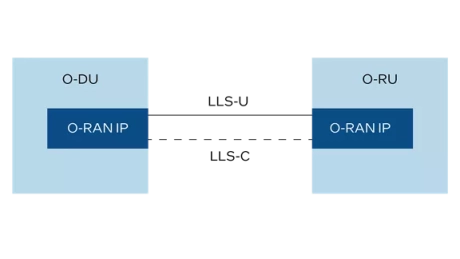

O-RAN Intel® FPGA IP

- The Extensible Radio Access Network (O-RAN WG4 Fronthaul Interface) defines a fronthaul interface between a lower-layer split distributed unit (DU) and remote unit (RU) in an Evolved Universal Terrestrial Access Network (E-UTRAN) and Next-Generation Radio Access Network (NG-RAN) system with a lower layer functional split-7-2x based architecture

- The O-RAN IP implements control and user plane protocol specified in O-RAN-FH.CUS.0-v03.00.

-

Low-Power ISP

- The Image Signal Processing (ISP)-- ISI700 receives camera sensor data via the 4-channel DVP interface

- It is designed for multi-camera, multi-exposure high dynamic range (HDR) image signal processor (ISP) for the mid- to high-end consumer and surveillance market

- The ISI700 offers the following functions: It brings advanced imaging technologies and chromatic aberration correction to provide unrivalled image quality and support to a large number of HDR sensor formats