SDXC3.0 Host IP

Filter

Compare

1,535

IP

from

139

vendors

(1

-

10)

-

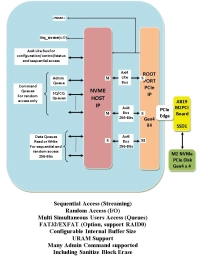

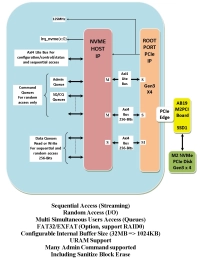

ARTIX Ultra Scale Plus NVME HOST IP – Gen4

- When using a PCIe RP IP configured in Gen4 the system frequency is at 250MHz/256-Bits.

- When using a PCIe RP IP configured in Gen3 the system frequency is at 125MHz/256-Bits.

-

Kintex Ultra Scale Plus NVMe Host IP

- The LDS NVME HOST IP has been done for beginners and expert in NVMe to drive NVMe PCIe SSD.

- The register file interface simplify the management of the IP for CPU interface or State Machine interface using AXI bus.

-

AGILEX 7 R-Tile Gen5 NVMe Host IP

- The LDS NVME HOST IP has been done for beginners and expert in NVMe to drive NVMe PCIe SSD.

- The register file interface simplify the management of the IP for CPU interface or State Machine interface using Avalon bus.

-

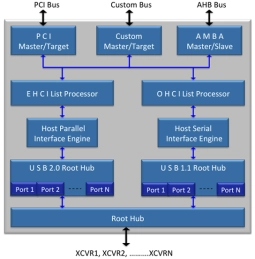

USB 2.0 Host IP Core

- The USB 2.0 Host IP is a USB 2.0 specification compliant host IP core with an optional AHB, PCI, or custom host interface.

- The USB 2.0 Host IP supports 480 Mbit/s in High Speed (HS) mode. 12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS) mode.

-

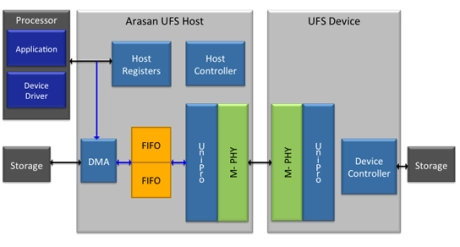

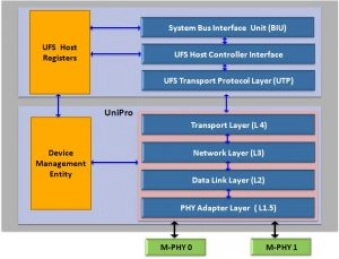

UFS 2.1 Host Controller IP

- JEDEC UFS 2.0 and UFS HCI 2.0 Compliant

- Supports high performance M-PHY v3.0 type-1

- 2 lanes @ 5.9 Gbps per lane

- UniPro v1.6 link layer

- Definable write-protect group size

-

UFS 3.0 Host

- UFS 3.0 Host and Device configurations available

- Complete UFS 3.0 hardware implementation

- Interop-proven UniPro 1.8 link layer

- MIPI M-PHY 4.0 Interface

-

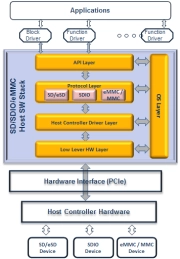

SD 3.0/SDIO 3.0/eMMC 4.51 Host Controller Software Stack

- This is a production-ready software stack for Arasan’s SD 3.0/ SDIO 3.0/ eMMC 4.51 Host Controller IP that is used to connect to SD, SDIO, or eMMC devices.

- The SD 3.0/eMMC 4.51 stack can also be used for validating a device during its development and integration life cycles thereby helping designers to reduce the time to market for their product.

-

SD Card Host Controller IP

- The SD Card Host IP f is a highly integrated host controller IP solution that supports three key memory card I/O technologies:

- The SD Card Host IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds.

-

eMMC Host Controller IP

- The eMMC Host controller IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds.

- The eMMC 4.51 Host IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead.

-

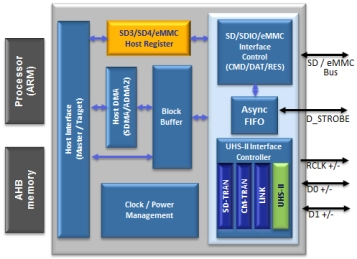

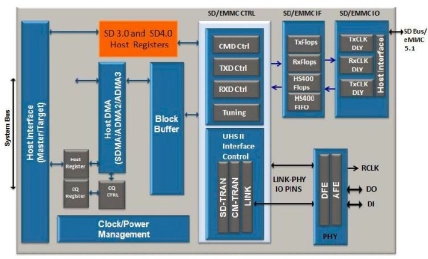

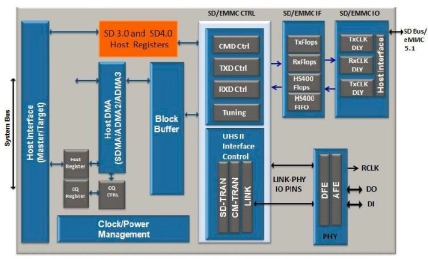

SD 4.1 / SDIO 4.1 / eMMC 4.51 Host Controller IP

- The SD 4.1/SDIO 4.1 IP from Arasan Chip Systems is a highly integrated host controller IP solution that supports three key memory card I/O technologies.

- SD 4.1 Host Controller IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds.