SD SDIO MMC controller IP

Filter

Compare

17

IP

from

8

vendors

(1

-

10)

-

SD / SDIO / MMC Host Controller

- Compliant with SD Host Controller Standard Specification Version 2.0

- Compliant with SD Physical Layer Specification Version 2.0

- Compliant with SDIO Specification 2.0

- Compliant with eMMC Specification Version 4.41

-

SD Host Controller IP, SD host spec. v3.0, SDIO spec. v2.0, MMC spec. v4.3, Supports UHS50/UHS104 card, Soft IP

-

SD Card Input/Output Protocol Controller

- Compliance with Embedded MultiMediaCard System Specification Version 4.51. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (backward compatibility)

- Full compliance with SD memory card specifications version 4.2 ( SPI mode and UHS-II mode not supported)

-

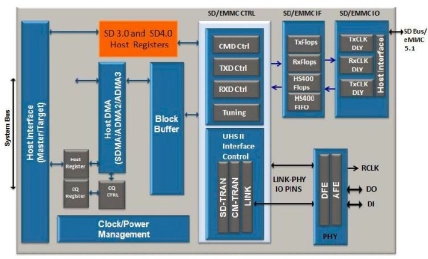

SD 3.0 / SDIO 3.0 / eMMC 5.1 Host Controller IP

- The SD 3.0 / eMMC 5.1 Host IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds.

- The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead.

-

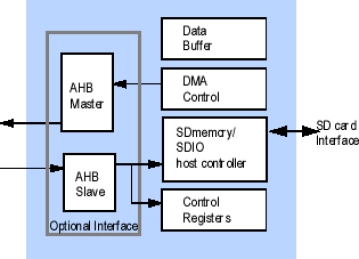

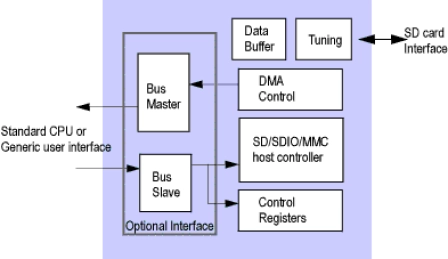

SD/SDIO 2.0 MMC Host Controller

- Host controller for SDIO, SD memory card, and MMC interface.

- Allows host CPU to access SD and MMC devices.

- Simple user interface optimized for on-chip bus connection.

- User interface supports 32-bit and 64-bit data.

-

SD Card Host Controller IP

- The SD Card Host IP f is a highly integrated host controller IP solution that supports three key memory card I/O technologies:

- The SD Card Host IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds.

-

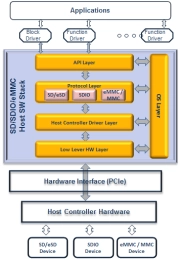

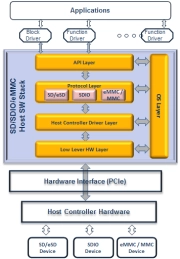

SD 4.1 Host Controller Software Stack

- This is a production-ready stack for Arasan’s eMMC Host Controller IP that is used to connect to SD, SDIO, or eMMC devices.

- The SD4/SDIO4/eMMC 4.5.1 Stack can also be used for validating a device during its development and integration life cycles thereby helping designers to reduce the time to market for their product.

-

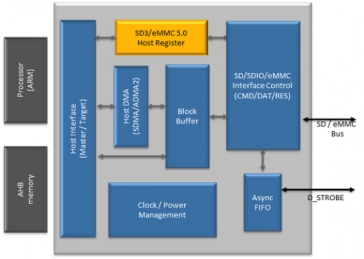

SD 3.0/eMMC 4.5 Host Controller

- Host controller for SD and SDIO 3.0 with options to support eMMC 4.41 interface.

- Allows host CPU to access SD and MMC devices.

- Simple user interface optimized for on-chip bus connection.

- Choices of AHB, AXI, APB, PLB, Wishbone, Avalon, SH4 and generic user interface.

-

SD 3.0/SDIO 3.0/eMMC 4.51 Host Controller Software Stack

- This is a production-ready software stack for Arasan’s SD 3.0/ SDIO 3.0/ eMMC 4.51 Host Controller IP that is used to connect to SD, SDIO, or eMMC devices.

- The SD 3.0/eMMC 4.51 stack can also be used for validating a device during its development and integration life cycles thereby helping designers to reduce the time to market for their product.

-

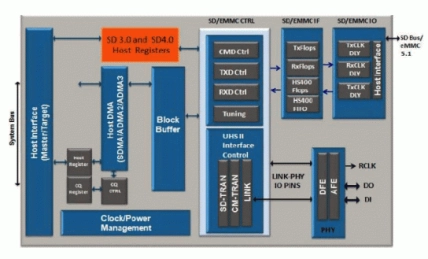

SD 4.1 eMMC 5.1 Dual Host Controller IP

- The SD 4.1/SDIO 4.0/eMMC 5.0 Host IP from Arasan Chip Systems is a highly integrated host controller IP solution that supports three key memory card I/O technologies:

- The SD 4.1 / eMMC 5.1 Host IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds. The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead. In addition, a host can utilize this IP to boot directly from an attached eMMC memory, thereby simplifying system initialization during power up. The host interface is based on a standard 32-bit AHB bus which is used to transfer data and configure the SD 4.1 / eMMC5.1 Host IP.

- eMMC 5.1 is backward compatible to the previous versions.