SD 5.1 eMMC 5.1 IP

Filter

Compare

50

IP

from

5

vendors

(1

-

10)

-

SD 4.1 eMMC 5.1 Dual Host Controller IP

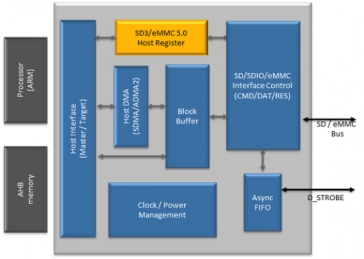

- The SD 4.1/SDIO 4.0/eMMC 5.0 Host IP from Arasan Chip Systems is a highly integrated host controller IP solution that supports three key memory card I/O technologies:

- The SD 4.1 / eMMC 5.1 Host IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds. The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead. In addition, a host can utilize this IP to boot directly from an attached eMMC memory, thereby simplifying system initialization during power up. The host interface is based on a standard 32-bit AHB bus which is used to transfer data and configure the SD 4.1 / eMMC5.1 Host IP.

- eMMC 5.1 is backward compatible to the previous versions.

-

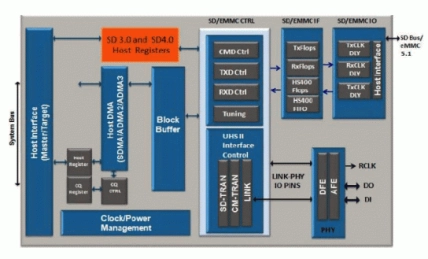

SD 3.0 / SDIO 3.0 / eMMC 5.1 Host Controller IP

- The SD 3.0 / eMMC 5.1 Host IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds.

- The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead.

-

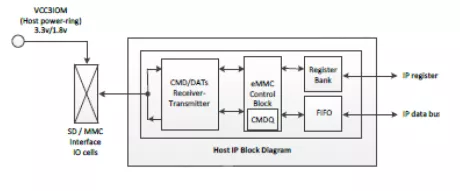

SD 5.1 / eMMC 5.1 Host Controller IP

- SD IP Features :

- Support SD system specification version 5.1

- Support Application Performance Class 1.

- Backward compatible to SD2.0 host

-

High-Density eMRAM Compiler TSMC 22ULL

- eMRAM compiler enabling low-power designs requiring high memory capacity

-

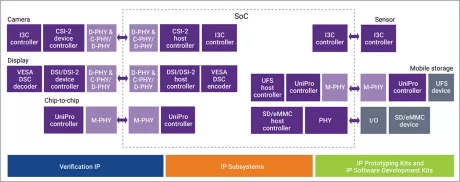

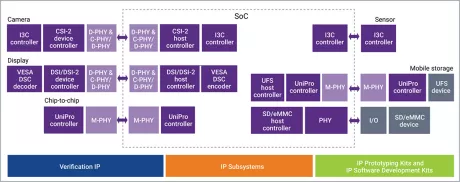

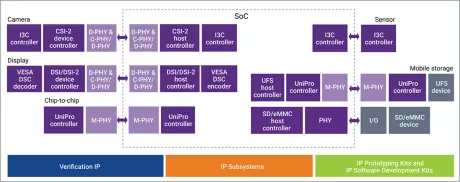

Low-power SD/eMMC host controller IP provides advanced high-performance 32- and 64-bit AXI interface to the SoC

- Compliant with SD HCI specification

- CQE capable of reordering task execution based on priority

- Data prefetching for back to back tasks—further improves random IOPS

- Low-power features with power gating and multi-power rails

-

SD/eMMC - TSMC 7FF, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 6FF, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 28HPM, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 28HPCP, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution