PHY Transceiver IP

Filter

Compare

655

IP

from

40

vendors

(1

-

10)

-

Serial ATA (SATA) PHY Transceiver IP

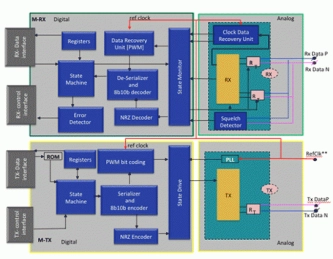

- SMS6000 is a fully integrated CMOS transceiver that handles the low level Serial ATA protocol and signaling.

- It contains all necessary Clock synthesis, Clock Recovery, Serializer, Deserializer, Comma detect for 8B/10B encoded data and Frame alignment functionalities.

-

PCI Express PIPE PHY Transceiver

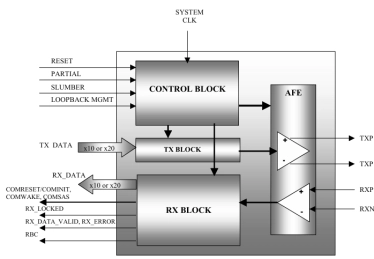

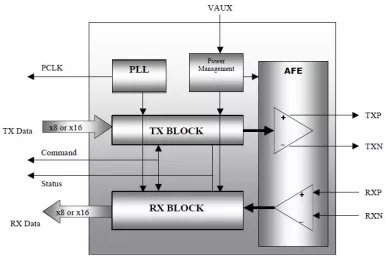

- Supports 2.5Gb/s serial data rate

- Utilizes 8-bit or 16-bit parallel interface to transmit and receive PCI Express data

- Full Support for Auxiliary Power (Vaux) for Energy aware systems like Multi-Port Host Controllers

- Data and clock recovery from serial stream on the PCI Express bus

-

Zigbee Transceiver PHY

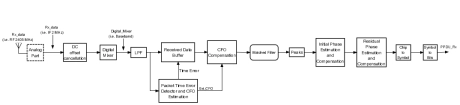

- Low power transceiver PHY IP for ZigBee applications, compliant with IEEE 802.15.4 standard.

- Efficient demodulator with frame synchronization and frequency offset compensation

- Supports 2 MHz IF input (reconfigurable on request)

- Offset-QPSK (OQPSK)

-

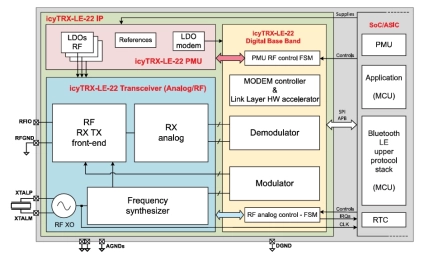

Bluetooth® Low Energy 6.2 PHY IP with Channel Sounding

- The icyTRX-LE-22 RF transceiver PHY IP delivers an optimal trade-off between power consumption and Bluetooth Low Energy (LE) RF performance — excellent sensitivity and strong interference rejection — while minimizing the overall cost for loT applications.

- Occupying just 0.57 mm2 in a 22 nm technology (7 metal layers), the analog RF portion of the IP integrates on-chip passives and Built-In-Self-Test (BIST) structures to drive down silicon area, wafer cost, bill of materials, and production-test expenses.

-

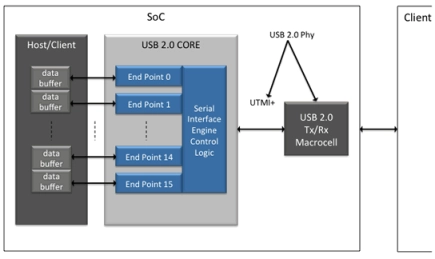

USB 2.0 HS PHY Interface

- The USB PHY IP is UTMI interface compatible and a dedicated circuit for full-function USB 2.0 transceivers.

- It is a mixed-signal circuit, with the analog part including the transmitting and receiving circuits, level conversion circuits, bus driver circuits, etc., and the digital part including the transmitting and receiving and speed switching control circuits, encoding and decoding circuits, serial-to-parallel and parallel-to-serial conversion circuits, as well as digital CDR circuits, etc.

-

USB 2.0 PHY IP core

- Complies with USB specifications, rev. 2.0 and 1.1

- Complies with UTMI+ specification, level 3, rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

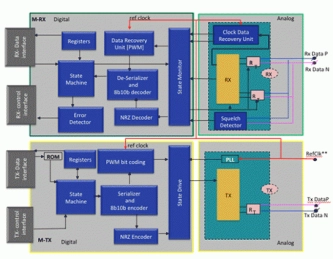

MIPI M-PHY® 3.1 Analog Transceiver

- The M-PHYs are of Type 1, which apply to UFS, LLI and CSI-3 protocols.

- The Multi-gear M-PHY 3.0 consists of analog transceivers, high speed PLL, data recovery units as well as the state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant to the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.

-

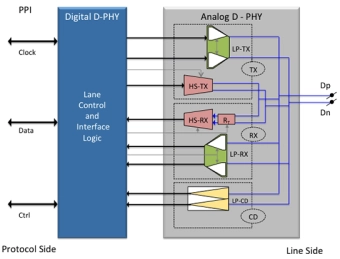

MIPI D-PHY Analog Transceiver IP Core

- The MIPI D-PHY Analog Transceiver IP Core is fully compliant with the D-PHY specification version 1.1.

- It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols at speeds up to 1.5Gbps per lane.

- It is a Universal PHY that can be configured as a transmitter, receiver, or transceiver.

-

MIPI M-PHY® 4.1 Analog Transceiver

- The M-PHY is of Type 1, which apply to UFS, LLI, and CSI-3 protocols. The Multi-gear M-PHY 4.1 consists of analog transceivers, high-speed PLL, data recovery units as well as state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant with the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.