Multiport Memory Controller IP

Filter

Compare

32

IP

from

15

vendors

(1

-

10)

-

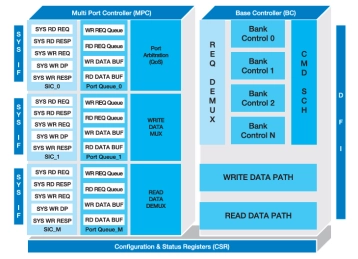

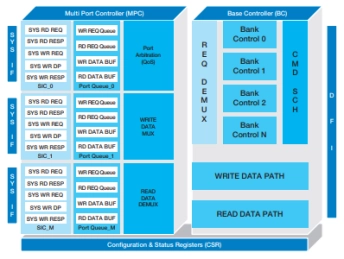

Universal Multi-port Memory Controller for RLDRAM2/3, DDR4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- The UMMC Controller is a highly flexible and configurable design. It is targeted for high bandwidth access and low power consumption such as next generation mobile, DDR/LPDDR networking and consumer applications.

- The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities.

-

Universal Multi-port Memory Controller for RLDRAM2/3, DDR5/4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- The UMMC (Universal Multi-port Memory Controller for RLDRAM2/3, DDR5/4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2) is a highly flexible and configurable design that supports RLDRAM2, RLDRAM3 and JEDEC compliant DDR5, DDR4 3DS, DDR4, DDR3, LPDDR3, LPDDR3 and LPDDR2 memories.

- It is targeted for high bandwidth access and low power consumption such as next-generation mobile, networking and consumer applications. The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities

-

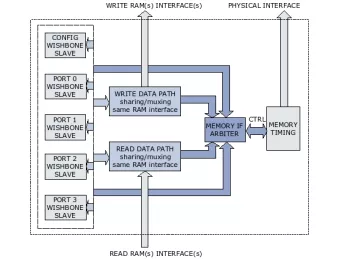

Multi-Port Memory Controller (DDR/DDR2/SDRAM)

- Soft Direct Memory Access (SDMA) support

- Double Data Rate (DDR/DDR2) and Single Data

- Rate (SDR) SDRAM memory support

- DIMM support (registered and unbuffered)

-

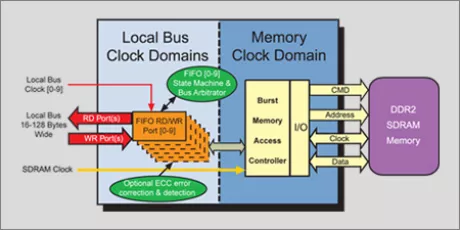

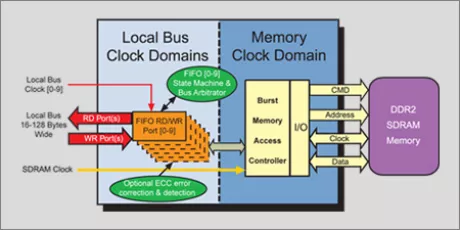

Avalon Multi-port DDR2 Memory Controller

- 200 / 333 MHz (400/666 Mbps) Cyclone/Stratix DDR2 memory performance

- DDR2 Memory Devices

- From 1 to 16 Avalon-MM local bus port interfaces

- Memory bandwidth utilization in excess of 95%

-

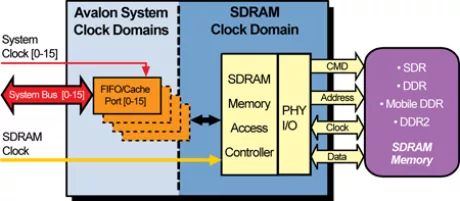

Streaming Multi-port SDRAM Memory Controller

- 200/333 MHz (400/666 Mbps) Cyclone / Stratix memory performance

- SDR, DDR, DDR2, and Mobile DDR SDRAM memory devices

- Up to 10 native RD or WR ports

- Memory data width: 8/16/32/64-bit

-

Avalon Multi-port SDRAM Memory Controller IP Core

- 200 / 333 MHz (400/666 Mbps) Cyclone / Stratix DDR2 memory performance

- SDR, DDR, DDR2 and Mobile DDR SDRAM Memory Devices

- From 1 to 16 Avalon-MM local bus port interfaces

- Memory bandwidth utilization in excess of 95%

-

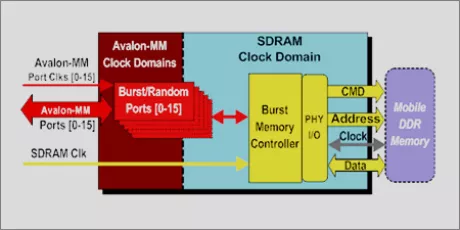

Avalon Mobile DDR Memory Controller

- 200 MHz Cyclone / Stratix memory performance

- Supports all standard Mobile DDR SDRAM devices

- 1 to 16 Avalon® independent local bus port interfaces

- Avalon Pipelined and Burst transfers

-

DO-254 DDR Memory Controller 1.00a

- DDR, DDR2, DDR3, and LPDDR (Mobile DDR) memory standards support

- Up to 800 Mb/s (400 MHz double data rate) performance

- Up to four MCB cores in a single Spartan-6 device

- Configurable dedicated multi-port user interface to FPGA logic

-

-

DDR5 Memory Controller IP with Advanced Feautures

- Supports DDR5 protocol standard JESD79-5 Specification.

- Compliant with DFI version 5.0 Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels