Motion Processing IP

Filter

Compare

38

IP

from

17

vendors

(1

-

10)

-

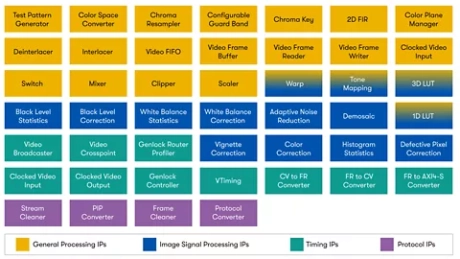

Video and Vision Processing Suite

- The Intel® FPGA Video and Vision Processing Suite is a collection of next-generation Intel® FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel® FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, industrial inspections and robotics, smart city/retail and consumer.

-

Video and Image Processing Suite

- The Intel FPGA Video and Image Processing Suite is a collection of Intel FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, smart city/retail, and consumer.

-

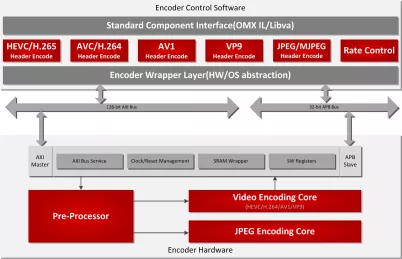

Microprocessor IP for video codecs and video processing -- High Number of Streams Encoder For Data Center

- Enables up to 256 streams encoding with high video quality single-core solution, or multi-core solution, supporting AV1, HEVC, H.264, VP9 video formats and JPEG.

-

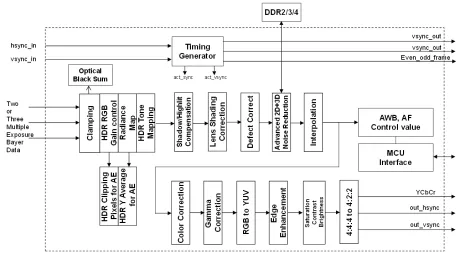

Multiple Pixel Processing Camera Image Signal Processing Core

- Support RGB Bayer progressive image sensor and Monochrome progressive image sensor

- Support 8 ~ 14 bit input data Bayer

-

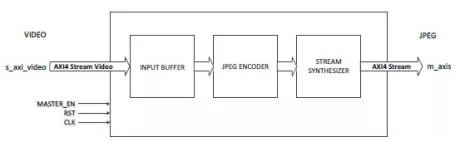

Motion JPEG Encoder

- Supports Xilinx® Zynq®-7000 AP SoC and 7 series FPGA families

- Compliant with the Baseline Sequential DCT mode of the ISO/IEC 10918-1 JPEG standard

-

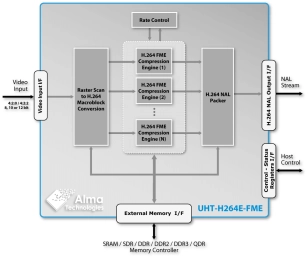

Scalable Ultra-High Throughput H.264 Encoder − Full Motion Estimation

- The UHT-H264E-FME core is a scalable, ultra-high throughput, hardware H.264 encoder, designed to enable 4K and 8K Ultra HD resolutions in power- and cost-effective FPGA or ASIC implementations.

- Powered by a highly-featured Full Motion Estimation engine, this encoder is the most advanced one of our UHT H.264 IP cores and offers best-in-class compression for applications needing advanced H.264 efficiency for high-quality, low-bitrate video encoding.

-

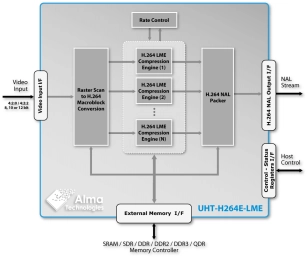

Scalable Ultra-High Throughput H.264 Encoder − Light Motion Estimation

- The UHT-H264E-LME core implements a simple and flexible, requests based, external memory interface with independent read and write data paths.

- The external memory I/F is also designed to be tolerant to memory delays and latencies, which may be present in a shared memory system architecture.

-

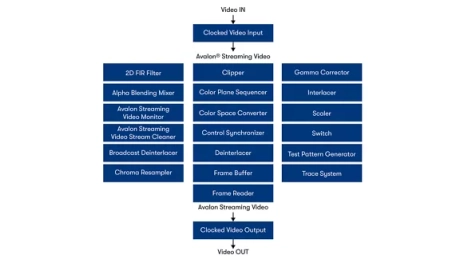

Video Processing Subsystem

- AXI Stream input and output interface

- Video resolutions up to UHD@60 fps (both at input & output interface)

- Features high quality Multi-tap poly-phase Scaler, Motion adaptive deinterlacer, Color space conversion, Chroma resampling, Letter box functions

- Video encoding RGB 4:4:4, YUV4:4:4, YUV 4:2:2 and YUV 4:2:0)

-

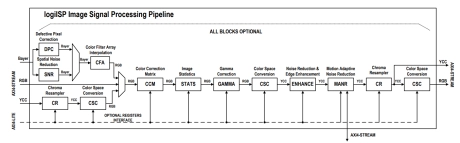

UHD Image Signal Processing (ISP) Pipeline

- The logiISP-UHD Image Signal Processing Pipeline IP core is an Ultra High Definition (UHD) ISP pipeline designed for digital processing and image quality enhancements of an input video stream in Smarter Vision embedded designs based on Xilinx ACAP, MPSoC, SoC and FPGA devices.

- It enables parallel processing of multiple Ultra HD video inputs in different programmable devices, ranging from the small Xilinx Artix®-7 FPGAs to the latest Xilinx Versal Adaptive Compute Acceleration Platform (ACAP) devices.

-

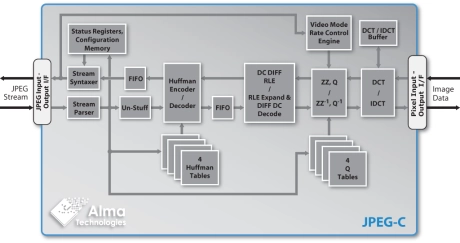

8-bit Baseline JPEG Codec with Optional Video Rate Control

- The JPEG-C core is a standalone and high-performance, half-duplex 8-bit Baseline JPEG Codec for still image and video compression applications.

- Full compliance with the Baseline Sequential DCT mode of the ITU-T T.81 JPEG standard makes this IP core ideal for interoperable systems and devices.

- The JPEG-C is available for ASIC or AMD-Xilinx, Efinix, Intel, Lattice and Microchip FPGA and SoC based designs.