MIL-STD-1553 IP

Filter

Compare

11

IP

from

9

vendors

(1

-

10)

-

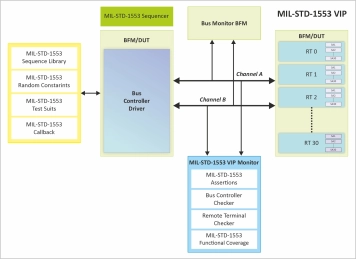

MIL-STD-1553 Verification IP

- Supports up to 31 Remote Terminals (devices).

- Supports up to 30 sub-addresses (sub-system).

- Supports multiple (commonly dual) redundant buses.

- Supports Dual Pins for multiple (commonly dual) redundant buses.

-

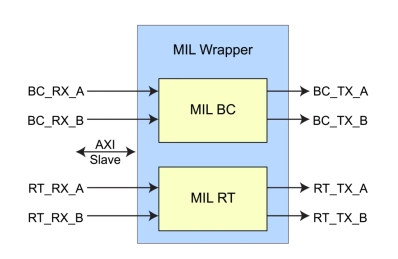

MIL-STD-1553 Bus Controller, Remote Terminal, and Monitor Terminal

- Mil-Std-1553 Intellectual Property for FPGAs and ASIC

- Suitable for any Mil-Std-1553 BC, RT, MT implementation

-

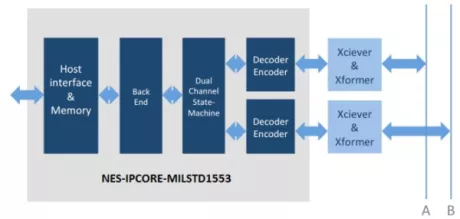

DO-254 compliant MIL-STD-1553B IP core

- MIL-STD-1553B IP Core implements MIL-STD-1553B standard and provides single or multi-functional interface between host processor and MIL-STD-1553 bus transceiver.

- DO-254 compliant MIL-STD-1553B IP core can function as Bus Controller (BC), two separate Remote Terminals (RT) and Bus Monitor (BM), simultaneously.

-

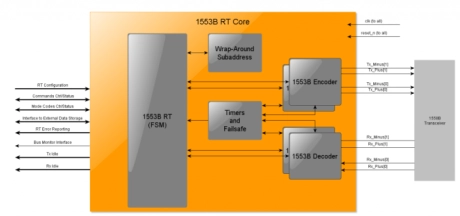

MIL-STD-1553B Remote Terminal DO-254 IP Core

- The 1553B RT Core implements a Remote Terminal as specified in the MIL-STD-1553B specification, including Notes 1 through 7.

- MIL-STD-1553B is the military specification defining a Digital Time Division Command/Response Multiplexed Data Bus operating at 1 Mbps.

- The 1553 databus is a dual-redundant, bidirectional, Manchester II encoded databus with a high bit error reliability.

-

Mil-Std-1553B/AS15531 Interface

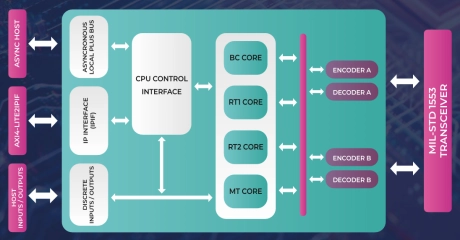

- The GR1553B core implements the MIL-STD-1553B (Notice 2) data bus protocol, with ability to serve as Bus Controller (BC), Remote Terminal (RT) or Bus Monitor (BM).

-

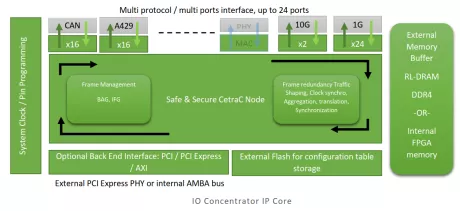

Multi Protocol IO Concentrator (RDC) IP Core for Safe and Secure Ethernet Network

- Ethernet/ARINC664P7 Switch with customizable number of ports up to 1 Gbps.

- Support IEEE 1588 PTPV2 as GrandMaster or User

- Safe & Secure Ethernet communication

- Multi-protocol : CAN, ARINC429, MIL-STD-1553, TSN

-

-

Configurable AMBA bus SoC platform

- Robust and fully synchronous single-edge clock designs

- Up to 125 MHz in FPGA and 400 MHz on 0.13 um ASIC technologies

- Fault-tolerant and SEU-proof version

- Symmetric Multi-processor support (SMP)

-

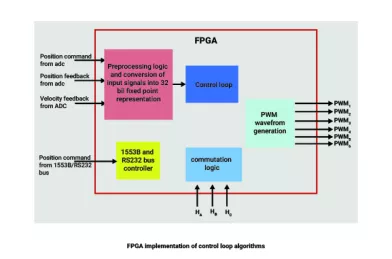

MIL1553B IP Core

- High bit error reliability

- Dual redundancy : Two buses supported

- BC, RT and BM Modes are supported.