IEEE 1588-2008 IP

Filter

Compare

38

IP

from

10

vendors

(1

-

10)

-

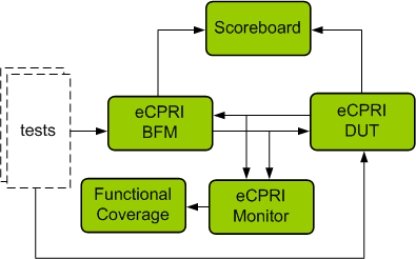

eCPRI Verification IP

- Compliant with eCPRI Specification V2.0.

- Complete eCPRI Tx/Rx functionality.

- Supports the eCPRI layer of the eCPRI specification.

- Supports 5G and enables increased efficiency.

-

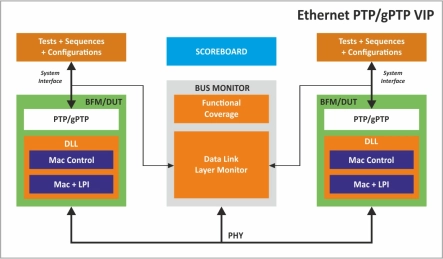

PTP/gPTP Verification IP

- Provides Ethernet fully compliant to 802.3-2018 supporting all media independent interfaces for (1/10/25/40/50/100/200/400/800 G)

- Provides PTP as per IEEE 1588-2008 specification

- Supports BMCA

- Supports PTP Delay Request Mechanism (Announce-sync-FollowUp-DelayReq-DelayResp)

- Supports PTP Peer Delay Mechanism (PdelayReq – PdelayResp - PdelayRespFollowUp)

- Supports Local Clock generation with user configurable start for timestamp generation

- Supports Master-Slave and slave only port state machines capable with support for all message timers

- Supports basic Management Messages with user control from test/sequence

- Supports one step and two step clock timestamping

- Supports BMCA

- Supports PTP Delay Request Mechanism (Announce-sync-FollowUp-DelayReq-DelayResp)

-

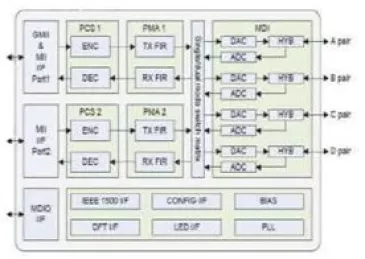

GbE (10/100/1000 Base-T) PHY IP, Silicon Proven in SAM 14LPP

- EEE 802.3-2008, IEEE 802.3az fully standards compliant

- IEEE 1588-2008 support

- BroadR-Reach™ support

- Dual port MAC interface:

-

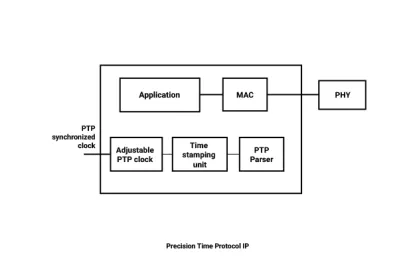

Precision Time Protocol IP

- Hardware support for IEEE 1588 PTP V1 and V2

- Taps path between MAC and PHY

- Full-duplex and half-duplex mode of operation

- PTP Timestamp Unit according to IEEE 1588-2008

-

HSR-PRP Switch

- Fast Ethernet (100Mb) and Gigabit (1GB) versions available

- It switches frames by hardware. This feature offers high switching speeds, needed to fulfill the Maximum Allowed Age and Data Integrity set for Process Bus and Inter-bay Bus in Electric Substation Automation

- The processing architecture has been designed specifically for HSR/PRP. Forwarding latencies in range of 500ns for Gigabit Ethernet

- It is an all-hardware. There is no need for on-chip microprocessor nor software stack

-

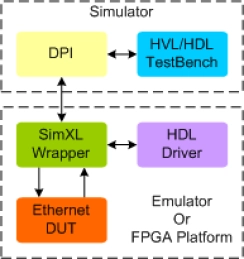

Ethernet Synthesizable Transactor

- Supports Full MII/RMII/SMII TX/RX functionality

- Supports Mac control and data frames support

- Ability to generate VLAN tagged and Priority tagged frames

- Supports Pause frame detection and generation

-

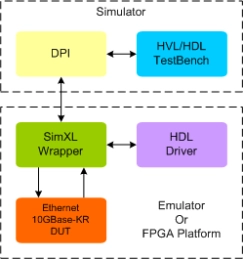

Ethernet 10GBase-KR Synthesizable Transactor

- Supports 10G as per 802.3:

- Supports XGMII

- Supports XTBI (i.e Output of 8b/10b PCS)

- Supports 10GBASE-KR with scrambler

-

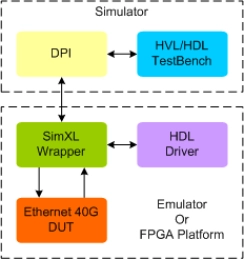

Ethernet 40G Synthesizable Transactor

- Supports 40G as per 802.3ba:

- Supports XLGMII

- Supports 40GBase-KR4/40GBase-CR4/40GBase-SR4/40GBase-LR4

- Supports 40GBase-R

-

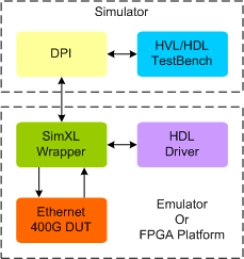

Ethernet 400G Synthesizable Transactor

- Supports 400G as per 802.3bs:

- Supports 400GBase_KR4

- Supports 400GBase_KR8

- Supports 400GBase_KR16

-

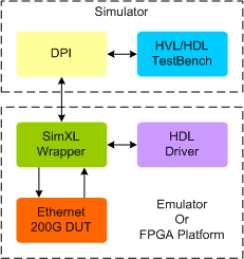

Ethernet 200G Synthesizable Transactor

- Supports 200G as per 802.3bs:

- Supports 200GBase_KR8

- Supports 200GBase_KR4

- Supports 200GBase_KR2