Forward Error Correction IP

Filter

Compare

168

IP

from

35

vendors

(1

-

10)

-

VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- VESA DisplayPort 1.4 compliant

- Reed-Solomon RS (254,250) FEC, 10-bit symbols

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode requires 2 FEC IP core instances)

- DisplayPort main 8b/10b encoder included (Tx only)

- Status and control can be done with signals or optionally via an integrated APB register module (Rx)

-

25G IEEE 802.3by Reed-Solomon Forward Error Correction

- Run-time switchable between IEEE802.3by and 25G Ethernet Consortium Schedule 3 specification mode

- Low latency

- Accessible as integrated feature in the 25G Ethernet Subsystem

- Configuration and status bus

-

50G IEEE 802.3 Reed-Solomon Forward Error Correction

- Low latency

- Accessible as an integrated feature in the 50G Ethernet Subsystem

- Configuration and status bus

- Selectable AXI4-Lite interface for status output

-

32G Fibre Channel (32GFC) Reed-Solomon Forward Error Correction

- Low latency design

- Configuration and status bus

- Example reference design demonstrating of RS-FEC and GT Wizard cores

- ECC RAM option

-

IEEE 802.3bj Reed-Solomon Forward Error Correction

- Low latency

- Supports 100 Gigabits

- Configuration and status bus

- Selectable AXI4-Lite interface for status output

-

-

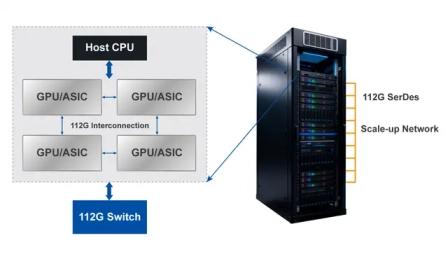

112G Multi-Rate SerDes

- Designed with a small footprint, ultra-low latency, and low power consumption, the 112G SerDes maximizes bidirectional memory access efficiency, reduces software complexity, and helps chip developers leverage existing Ethernet infrastructure to significantly lower Total Cost of Ownership (TCO).

- Featuring IEEE 802.3-compliant Forward Error Correction (FEC), 35dB ultra-high channel loss compensation, and adaptive high-speed equalization technologies (CTLE, FFE), it provides full-cycle link protection—from error correction to pre-warning—enabling highly compatible, stable, and efficient chip-to-chip connectivity solutions.

-

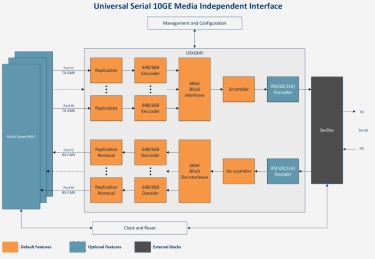

Universal Serial 10GE Media Independent Interface (USXGMII)

- The USXGMII PCS IP provides the logic required to integrate a USXGMII-M IP into any system on chip (SoC).

- Link speeds of 5G, 10G, or 20G are supported. Compliant with the Cisco Universal SXGMII Interface for multiple Multi-Gigabit Copper Network Ports and IEEE 802.3 Clause 49 standards, the PCS IP has several optional features to customize the physical coding sublayer (PCS) for the specific needs of any application.

-

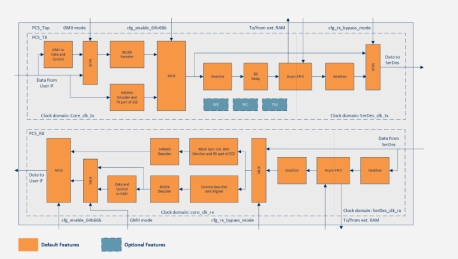

Ethernet PCS 1G/2.5G/5G/10G/25G & CPRI 7.0

- A combined silicon agnostic implementation of the PCS layer compliant with Ethernet standard IEEE 802.3-2018 and CPRI Specification V7.0 based solution

- The IP-core supports 1G, 2.5G, 5G, 10G, and 25G Ethernet data rates as well as CPRI data rate option 1 (614.14M) to option 10 (24.33024G).

-

DVB-S2-LDPC-BCH

- Irregular parity check matrix

- Layered decoding

- Minimum sum algorithm

- Soft decision decoding

- BCH decoder works on GF (2m) where m=16 or 14 and corrects up to t errors, where t = 8, 10 or 12