Ethernet MAC PCS IP

Filter

Compare

234

IP

from

30

vendors

(1

-

10)

-

100 G Ethernet MAC & PCS IP Core

- The 100 Gbps Ethernet IP solution offers a fully integrated IEEE802.3ba compliant package for NIC (Network Interface Card) and Ethernet switching applications.

- Ethernet IP solution implements two user (application) side interfaces. The register configuration and control port is a 32-bit AXI4-Lite interface.

-

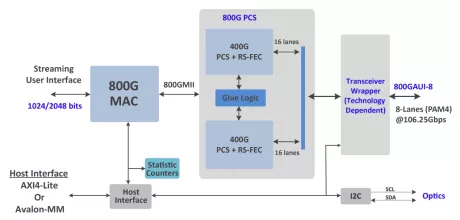

800 Gigabit Ethernet MAC + PCS

- Two 400GBase-R PCS cores with required modifications and glue logic.

- Includes RS-FEC(544,514) KP4 FEC

-

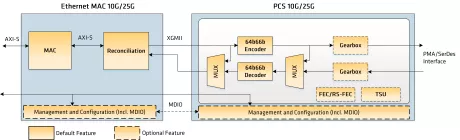

Ethernet MAC & PCS 10G/25G

- Richly Featured

- Delivering Performance

- Highly Configurable

- Silicon Agnostic

-

25G Ultra Low latency, 64-bit Ethernet MAC + PCS Solution (64-bit and 128-bit UI)

- MAC Core Features

- PCS Core Features

-

100G Only 320-bit Ethernet MAC + PCS @ 312.5MHz Solution; 4x25

- MAC Core Features

- PCS Core Features (Common)

- PCS Core Features (CAUI-4 Option)

- PCS Core Features (CAUI-10 Option)

-

100G Only 320-bit Ethernet MAC + PCS @ 312.5MHz Solution; 10x10

- MAC Core Features

- PCS Core Features (Common)

- PCS Core Features (CAUI-4 Option)

- PCS Core Features (CAUI-10 Option)

-

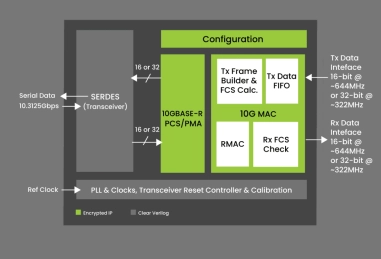

10-Gbps Ultra-Low Latency Ethernet MAC and PCS

- The core is designed using advanced design techniques leading to unmatched ultra-low gate count utilization and amazing latency performances.

- The 10G IP core support both 16b (644MHz) and 32b (322MHz) modes, and can support full wire line speed with a 64-byte packet length. It also supports back-to-back or mixed length traffic with no dropped packets.

-

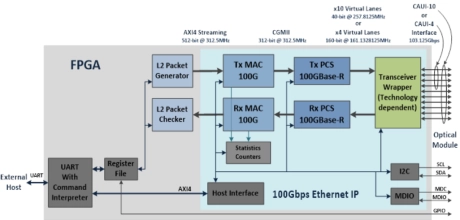

100G Ethernet Solution (MAC + 100GBase-R PCS)

- Implements the full 802.3 specification with preamble/SFD generation, frame padding generation, CRC generation and checking on transmit and receive respectively.

- Implements 802.3bd specification with ability to generate and recognize PFC pause frames (optional)

- Implements reconciliation sublayer functionality with start and terminate control characters alignment, error control character and fault sequence insertion and detection.

- Implements Deficit Idle Count (DIC) mechanism to ensure maximum possible throughput at the transmit interface.