EAI Design Services IP

Filter

Compare

98

IP

from

35

vendors

(1

-

10)

-

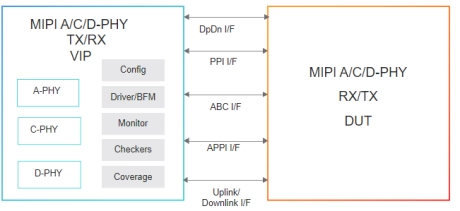

Simulation VIP for MIPI D-PHY, C-PHY and A-PHY

- PHY Monitor

- Built-in scoreboarding between serial/PPI interface, also monitors error signal interface

- Reports any detected error on any lane on serial interface and is not reflected on PPI interface

- C-PHY and D-PHY

-

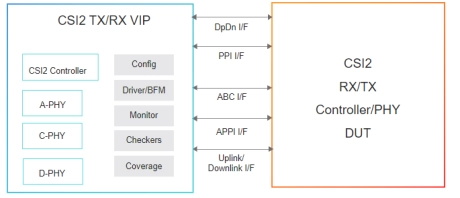

Simulation VIP for MIPI CSI-2

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection at CSI-2, D-PHY, C-PHY and A-PHY levels

- Callbacks access at multiple TX and RX queue points for scoreboarding and data manipulation

-

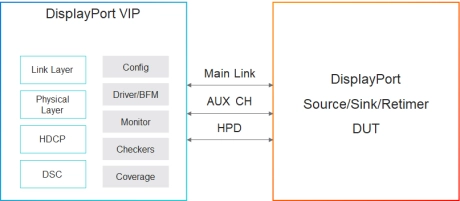

Simulation VIP for DisplayPort

- Device Support

- Source, Sink, Link Training-Tunable PHY Repeater (LTTPR/retimer)

- Main Link Interface

- Serial, Parallel (10-bit, 20-bit, 40-bit)

-

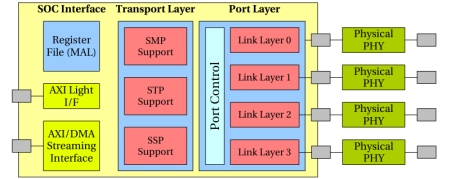

SAS Initiator, 12G, 4 Ports, 48 Gbps

- The SAS Initiator Controller IP Core provides an interface to high-speed serial link replacement for the parallel SCSI attachment of mass storage devices.

- Maximum supported bandwidth is 48 Gbps. The serial link employs multiple high-speed gigabit transceivers.

-

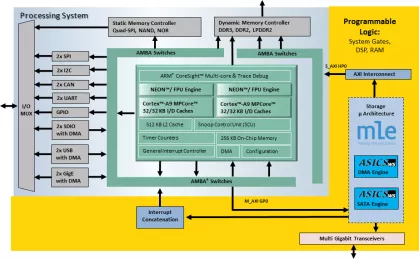

Zynq SATA Storage Extension - Production Reference Design

- Provides one single SATA I (1.5 Gbps), SATA II (3 Gbps) and SATA III (6 Gbps) host port.

- Access one single SATA HDD or SATA SSD via a standard Linux block device interface and Linux filesystems.

- Fully integrated and tested SATA I/II/III Host Controller IP Core.

- Fully integrated and tested DMA Controller IP Core.

-

MMC Device IP Core

- Compliant with MultiMediaCard Spec ver4.X/3.X

- Supports MMC 1bit, 4bit, 8bit modes, as well as SPI mode

- Maximum data rate up to 416Mbits/sec

- All command and response types are supported

- Supports Interrupt-mode (Wait-IRQ)

-

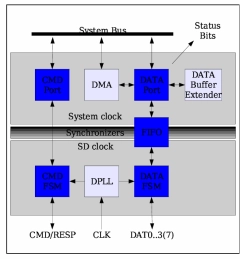

SD/SDIO Device IP Core

- A compact low power and scalable IP core which provides a simple, firmware-friendly cost-effective Physical Link interface for memory, i/o and combo devices, such as SD-based memory cards, Mini SD, Micro SD, SDIO Bluetooth devices, SDIO GPS, etc.

- The SD/SDIO Device IP core is designed for an easy integration with any card controller and any system bus, with minimum firmware development overhead.

-

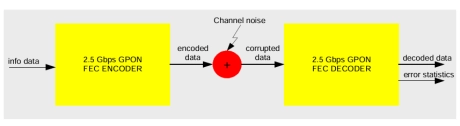

2.5 Gbps GPON FEC Codec

- This high performance core is a full featured Forward Error Correction encoder and decoder, specially designed for high speed optical networks or any other broadband applications.

- It is fully compliant with the 2.5 Gbps GPON standard (G.984.3) and is available for FPGA or ASIC implementation.

- The FEC algorithm is based on Reed-Solomon (255,239) code and consists of an encoder and decoder module.

-

I2C Master and Slave

- I2C is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices.

- It is most suitable for applications requiring occasional communication over a short distance between many devices.

-

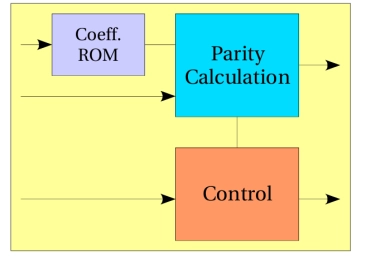

Reed Solomon Encoder IP Core

- Supports many different Reed-Solomon coding standards

- Code rate can be dynamically varied

- Parameterizable bits per symbol (M)

- Programmable codeword length (NVAL) with parameterizable maximum value (N)

- Programmable number of errors (TVAL) with parameterizable maximum value (T)