Die-to-Die PHY IP

Filter

Compare

68

IP

from

12

vendors

(1

-

10)

-

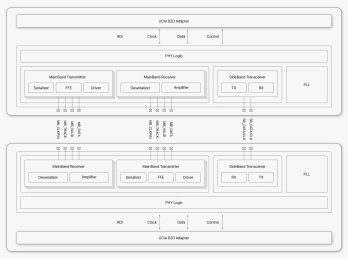

UCIe PHY (Die-to-Die) IP

- Compliant with UCIe v2.0, supporting 4/8/12/16/24/32GT/s data rates

- for Standard Package up to 16 lanes / for Advanced Package up to 64 lanes

- Provides a 1024-bit data bus width with high-throughput die-to-die communication

- Includes automatic per-lane calibration and optional transmitter de-emphasis

-

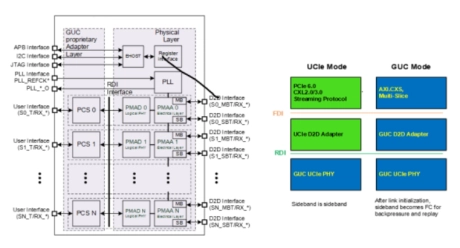

TSMC CLN5FF GUCIe LP Die-to-Die PHY

- IGAD2DY11A is an LP (Low Power) Die-to-Die (D2D) PHY for SoIC-X Face-to-Face advanced package.

- This GUCIe PHY not only supports UCIe specification rev 1.1 compliance physical layer and Raw D2D interface (RDI) but also optionally provides the

-

TSMC CLN3FFE GLink 2.3LL Die-to-Die PHY

- 56 full-duplex lanes per slice

- 6-Slice/2-Slice PMA included in the analog hard macro

- Lane repair

-

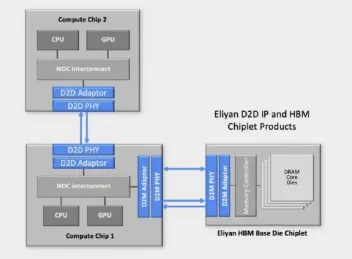

Die-to-Die PHY

- The NuLink technology delivers low-power and high-performance D2D IP core products, which support multiple industry standards and are available on both standard and advanced packaging.

-

TSMC CLN5FF GLink 2.0 Die-to-Die PHY

- 32 full-duplex lanes per slice

- 8 slices are included in the analog hard macro

- 1:8 mode with 256-bit data width or 1:16 mode with 512-bit data width for user interface

- VALID and READY handshake mechanism

-

TSMC CLN5FF GLink 2.3LL Die-to-Die PHY

- 56 full-duplex lanes per slice

- 8 slices are included in the analog hard macro

- 1:8 mode with 448-bit data width or 1:16 mode with 963-bit data width for user interface

- VALID and READY handshake mechanism

-

TSMC CLN7FF GLink-3D Die-to-Die Slave PHY

- Supports SoIC (3DFabric) CoW and WoW assembly

- Supports face to face and face to back with the same GDSII

-

TSMC CLN5FF GLink-3D Die-to-Die Master PHY

- Supports SoIC (3DFabric) CoW and WoW assembly

- Supports face to face and face to back with the same GDSII

- Supports point to multi-point (multi-Slave) communication

- Up to 5 Gbps/bond (2.5 GHz DDR) data rate

-

TSMC CLN6FF/7FF Die-to-Die Interface PHY

- 32 full-duplex lanes per slice

- 8 slices are included in analog hard macro

- Lane repair

-

Die-to-Die, AIB 2.0 PHY Ported to Intel 16, North/South (vertical) poly orientation

- Delivers up to 4Gbps per pin with up to bidirectional 2 Tbps/mm of die edge

- High-bandwidth, low-power, low-latency multi-channel PHY in applications requiring connections between dies within a package

- Compliant with Intel Advanced Interface Bus (AIB) v1.1 standard

- Compliant with IEEE 1149.1 (JTAG), 1149.6 (AC JTAG) for easy integration with SoC testability framework