DRBG IP

Filter

Compare

11

IP

from

6

vendors

(1

-

10)

-

-

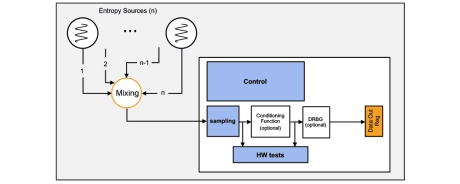

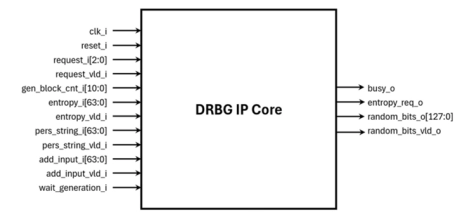

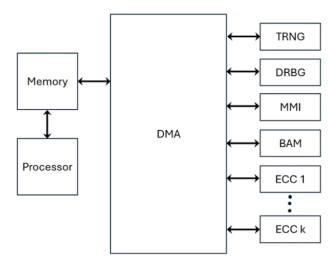

Deterministic Random Bit Generator (DRBG)

- The Deterministic Random Bit Generator is an essential silicon-proven digital IP core for all FPGA, ASIC and SoC designs that targets cryptographically secured applications.

- It is a deterministic algorithm compliant with the NIST-800-90A Rev1.

- The IP Core successfully passed NIST-800-90A Rev1 test suites and it is compliant with the FIPS-140-2 validation.

-

RSA Keygen IP Core

- RSA Keygen IP Cores perform key generation in compliance with the RSA Key Pair Generation specifications defined in 'FIPS 186'.

- This standard specifies methods for generating RSA key pairs.

- RSA Keygen IP Cores support key pair generation up to 4096 bits.

-

ECDSA IP Core

- ECDSA IP Cores perform digital signature generation and verification in compliance with the Elliptic Curve Digital Signature Algorithm (ECDSA) specifications defined in 'FIPS 186'.

- This standard specifies methods for digital signature generation and verification using the Elliptic Curve Digital Signature Algorithm (ECDSA).

-

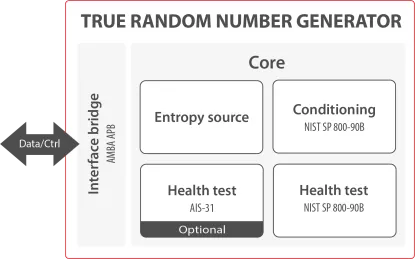

Fast NIST ESV certified, FIPS (SP800-90A/B/C) True Random Number Generator

- The TRNG-IP-77 is a FIPS-compliant and certified IP core for True Random Number Generation (TRNG) with an optional post-processor and several internal self-tests.

- Designed for easy integration into ASICs and SOCs, the 100% digital standard cell based TRNG-IP-77 provides a reliable and cost-effective embedded IP solution for our customer’s SoCs.

-

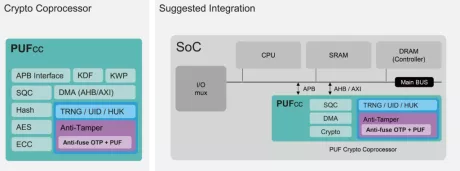

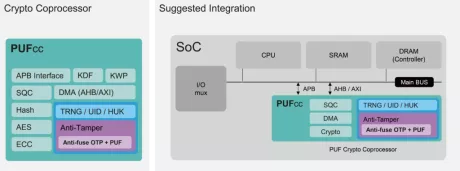

TLS 1.3 Compliant Crypto Coprocessor

- NIST CAVP certified and OSCCA standard compliant crypto engine suite

- Includes private/public key ciphers, message authentication code, hashes, and key derivation

- Key wrapping function for the secure export of keys

- Public-key coprocessor for digital signatures and key agreements over elliptic/Edward curves

-

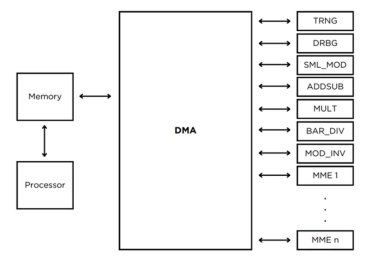

Crypto Coprocessor

- Comprehensively support all CPU architectures

- Crypto engine collective, consisting of private key cipher, message authentication code, hash, and key derivation functions that are NIST CAVP certified and OSCCA standards compliant

- Key wrapping function aiding the export of keys for external use

-

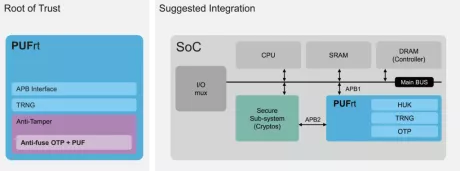

Hardware Root of Trust IP

- Built-in standard APB controller with privilege control to create secure/non-secure separation. Additionally, interface customization is available for different design requirements.

- Four 256-bit hardware PUF chip fingerprints, include a self-health check that can be used as a unique identification(UID) or a root key(seed).

- High-quality true random number generator (TRNG)

- 8k-bit mass production OTP with built-in instant hardware encryption (customization available)

-

NIST ESV certified, AIS-31, FIPS (SP800-90A/B/C) True Random Number Generator

- Non-deterministic Random Number Generator, FIPS-140 SP800-90A/B compliant, ESV certified for NRBGs and DRBGs (#E167).

- High performance, low power, fully digital, standard cell only, supports all CMOS nodes.

- Available as standalone RBG or embedded in the Rambus RT-130, RT-630, RT-660 Root of Trusts