DES IP

Filter

Compare

9,024

IP

from

372

vendors

(1

-

10)

-

Cryptographic engine using the DES, Triple-DES or AES

- The cryptographic processor (CRYP) can be used both to encrypt and decrypt data using the DES, Triple-DES, AES or SM4 algorithms.

-

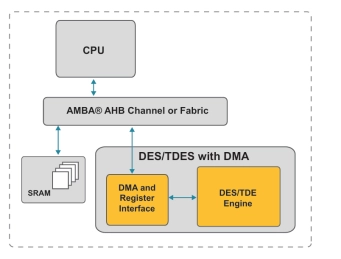

AHB DES and Triple DES with DMA

- The AHB DES/TDES Encryption/Decryption Engine is a configurable core that interfaces to an AHB microprocessor bus.

- The Controller encrypts or decrypts blocks of data based on the DES encryption standard.

- In order to accommodate a wide variety of system requirements, the Engine can be generated in two modes: LowLatency and LowGateCount. For a TDES system, three DES cores are instantiated.

-

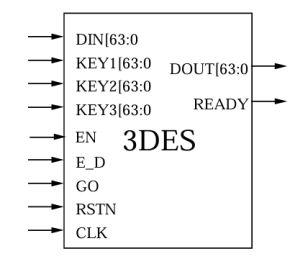

Triple DES core

- Implemented according to the X9.52 standard

- Implementation based on NIST certified DES core

- Also available in CBC, CFB and OFB modes.

- 112 or 168 bits keys supported.

-

DES Encryption and Decryption Processor

- Fully compliant 56-Bit key DES implementation

- Single DES operation

- Encryption and decryption are performed in 16 clock cycles

- Suitable for ECB, CBC, CFB and OFB implementations

-

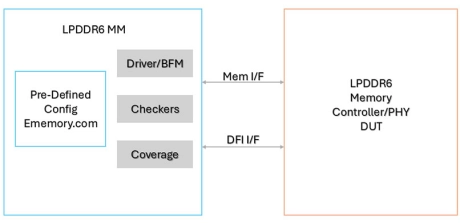

Simulation VIP for LPDDR6

- This Verification IP (VIP) is intended for modeling the upcoming JEDEC Low-Power Memory Device, LPDDR6 design specification.

- It provides a mature, highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification.

-

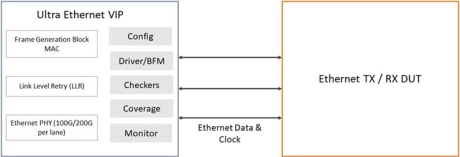

Simulation VIP for Ethernet UEC

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Callbacks access at multiple TX and RX queue points for scoreboarding, data manipulation, and error injection

- Transaction Tracker: Configurable tracking of all the transactions on the channels

-

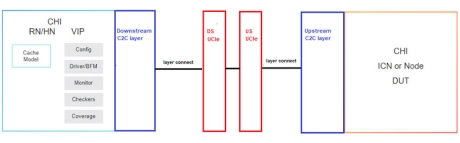

Simulation VIP for AMBA CHI-C2C

- Incorporating the latest protocol updates, the Cadence Verification IP for CHI-C2C provides a complete bus functional model (BFM), integrated automatic protocol checks, and a coverage model.

- Designed for easy integration in testbenches at IP, systems with multiple CPUs, accelerators, or other device chiplets, the VIP for CHI-C2C provides a highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms.

-

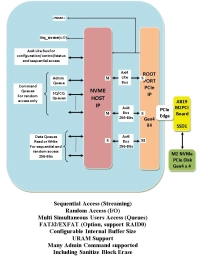

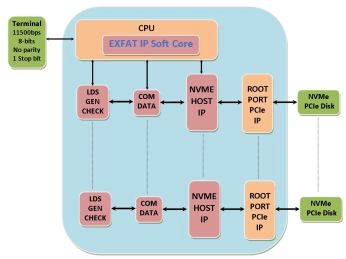

EXFAT IP Soft Core for NVMe

- Able to manage several disk in RAID0

- Same speed as in raw data format

- Support only 512-Byte LBA unit

- Support any disk size

-

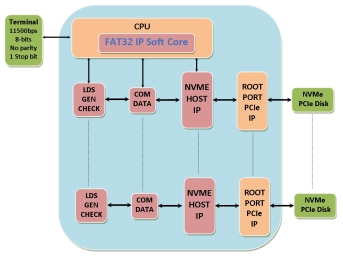

FAT32 IP Soft Core for NVMe

- Able to manage several disk in RAID0

- Same speed as in raw data format

- Support until 2TB disk size

- One directory per recording session

- One session file available to describe the recording session

-

ARTIX Ultra Scale Plus NVME HOST IP – Gen4

- When using a PCIe RP IP configured in Gen4 the system frequency is at 250MHz/256-Bits.

- When using a PCIe RP IP configured in Gen3 the system frequency is at 125MHz/256-Bits.