CXL IP

Filter

Compare

254

IP

from

23

vendors

(1

-

10)

-

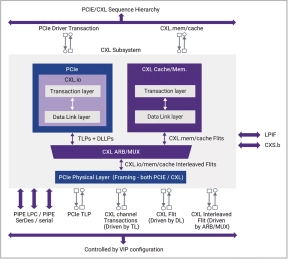

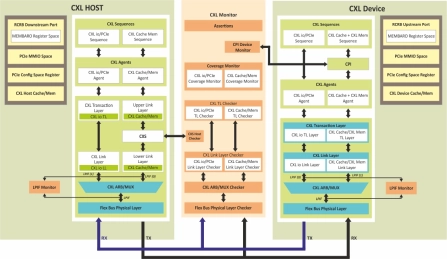

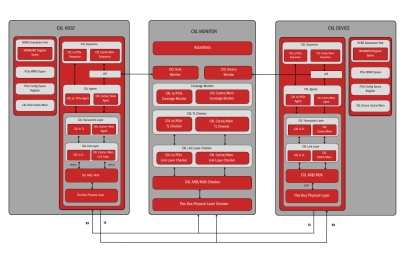

CXL 4 Verification IP

- Compliant with the CXL 4, 3.2, 2.0 & 1.1 Specifications.

- Support for all three protocols CXL.IO, CXL.CACHE & CXL.MEM including all CXL device types

- Support for PCIE Mode & Alternate Protocol Negotiation for CXL Mode

- Support for 256B flit in 128GT/s with PCIe Gen 6 as well as 64/32/16/8 GT/s speeds with backward compatibility.

-

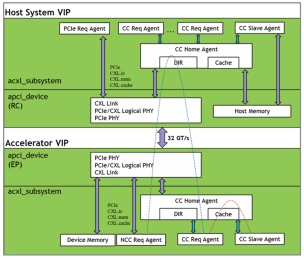

VIP for Compute Express Link (CXL)

- Native SystemVerilog/UVM

- Source Code Test Suites Available

- Built-in Protocol Checks

- Complete Subsystem Verification Solution

-

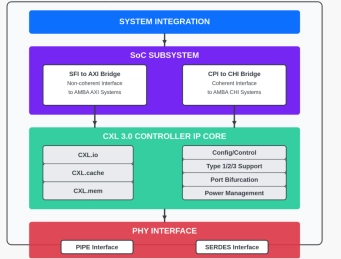

CXL 3.0 Controller

- The CXL Controller IP is micro-architected with power, performance, and area optimization for high bandwidth, minimum latency, and low power applications.

- The CXL IP supports seamless transition from FPGA prototyping to production silicon implementation.

- Featuring native integration with SignatureIP's Coherent and Non-coherent Network-on-Chip (NoC) IPs, this controller enables robust SoC subsystems and complete platform solutions

-

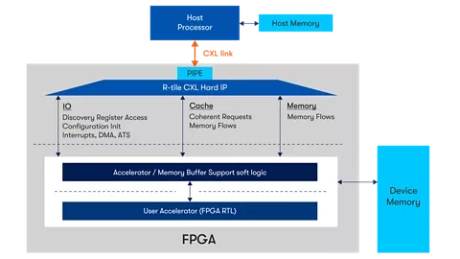

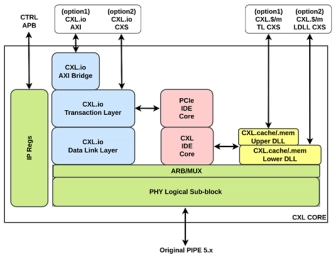

CXL Controller

- Compliant with CXL Specification version 2.0/1.1 and PCIe Base Specification 5.0 (32 Gbps per lane)

- Complaint with PIPE 5.x interface

- Supports X16, X8, X4, X2 and X1 lane widths

- Supports 512, 256 and 128 Data path widths

- Supports PCI Express Alternate Protocol

-

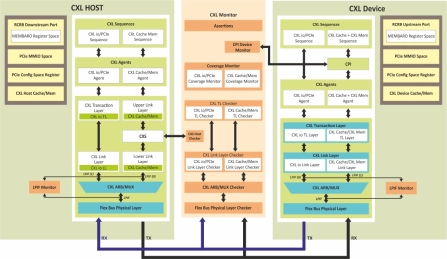

CXL 4.0/3.2/3/2 Verification IP

- Compliant with the CXL 3.2, 2.0 & 1.1 Specification.

- Support for all three protocols CXL.IO, CXL.CACHE & CXL.MEM including all CXL device types

- Support for PCIE Mode & Alternate Protocol Negotiation for CXL Mode

- Support for 256B flit in 64GT/s with PCIe Gen 6 as well as 32/16/8 GT/s speeds with backward compatibility.

-

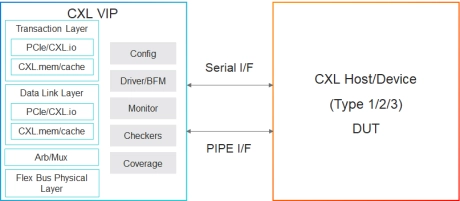

Verification IP for CXL

- Accelerated confidence in simulation-based verification of RTL designs with Compute Express Link (CXL) interfaces: CXL1, CXL2, CXL3, CXL3.1

-

Compute Express Link (CXL) FPGA IP

- Industry's first FPGA-based hardened CXL IP solution for Type 1, 2, and 3 devices.

- First FPGA to pass CXL Consortium Compliance Program (up to 32 GT/s speed).

-

CXL - Enables robust testing of CXL-based systems for performance and reliability

- CXL Verification IP is a cutting-edge solution for validating designs based on the Compute Express Link (CXL) protocol. With features like protocol compliance checks, cache coherency validation, and advanced debugging tools, it ensures robust and efficient testing of high-performance computing systems.

- From HPC and AI to automotive and edge computing, CXL Verification IP supports diverse applications. It enables seamless communication between processors, memory, and accelerators, ensuring reliable performance in data centers, ML systems, cloud infrastructures, and telecom networks.

-

CXL Controller IP

- The CXL/PCIe Controller IP carries out CXL 3.0 specification and is backward compatible to CXL 2.0 and 1.1.

- Possessing high customizability and supportability, this controller provides a comprehensive CXL solution.

-