BCH IP

Filter

Compare

78

IP

from

25

vendors

(1

-

10)

-

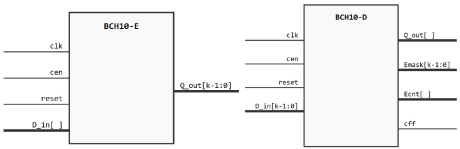

Very Low Latency BCH Codec

- High performance, low latency

- Small size (75K gates for k=298, t=4) configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

- Data inputs and outputs have flip-flops attached to the pins

-

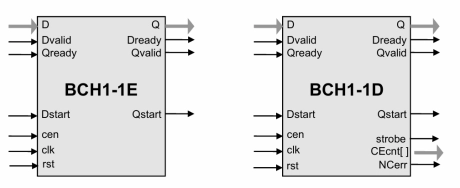

Parameterizable compact BCH codec

- Highly parameterizable

- Very low area (in the largest, n = 511 t = 16 configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

-

NavIC BCH Decoder

- Compliant with 'ISRO-NAVIC-ICD-SPS-L1-1.0' standard [1].

- Supports the BCH decoding for subframes 1 (TOI) signal.

- Throughput matching the required specifications.

- Bit-error-rate and block-error-rate performance meet the required specifications.

-

BCH ECC Core IP

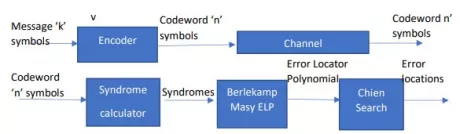

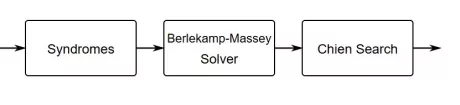

- The patent-pending Dynamically Configurable BCH technology is the base for the BCH ECC engine incorporating BCH coders and decoders configurable for a wide range of code-length for high performance and high data rate error corrections.

- The BCH ECC engine with configurable code-length BCH coders and decoders performs the Inversion-less Berlekamp-Massey Algorithm (IBMA) to generate or decode the ECC code on each clock.

-

BCH Intel® FPGA IP Core

- The Bose, Chaudhuri, and Hocquenghem (BCH) error correction intellectual property (IP) core is typically used in NAND flash applications

- The BCH Intel FPGA IP core is often used as a companion code with other forward error correction (FEC) IP cores, such as the Reed-Solomon and low-density parity-check (LDPC) IP cores.

-

DVB-S2X Wideband LDPC/ BCH Encoder

- Compliant with ETSI EN 302 307’

- Compliant with ETSI EN 302 307-2’

- Supports BCH-LDPC all code rates for digital video broadcasting

-

-

DVB-S2X Wideband LDPC/ BCH Decoder

- The DVB-S2X Wideband LDPC Decoder is a powerful FEC core decoder for Digital Video Broadcasting via Satellite.

- It implements extensions to the DVB-S2 design for better performance and efficiency as well as robust service availability.

-

BCH Error Correcting Code ECC

- Asynchronous operation

- No clocks required.

- No storage like memories SRAMS/ROMS/FilipFlops used

- No iterative Feedback in the pipeline