MIPI RFFE IP

Welcome to the ultimate MIPI RFFE IP hub! Explore our vast directory of MIPI RFFE IP

All offers in

MIPI RFFE IP

Filter

Compare

15

MIPI RFFE IP

from

5

vendors

(1

-

10)

-

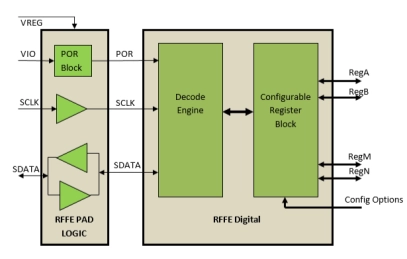

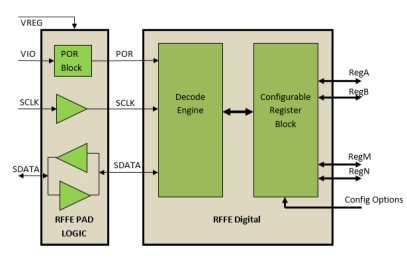

RFFE Slave IP Core

- Compliant with MIPI’s RFFE specification Rev 3.0

- Small silicon footprint

- Scalable Implementation

- Up to 15 Devices can be connected per Bus

- Low pin count on Interface side (SCLK and SDATA)

-

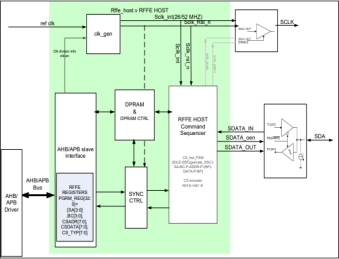

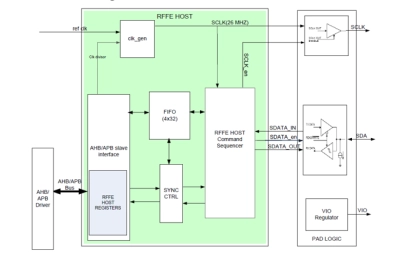

RFFE Master IP Core

- Compliant with MIPI RFFE Specification 3.0

- Delivered in Reuse Methodology Manual (RMM) compliant Verilog RTL format

- Optionally delivered as a physical design

- Small footprint

-

2.0 RFFE Slave IP

- The RF Front End (RFFE) control interface is defined to offer a common Interface for controlling RF front-end devices.

- Most commonly used Front-End devices include Power Amplifier, Low-Noise Amplifiers, Filters, Switches, Power Management Modules, and Antenna Sensors etc. These Functions can be residing in the same chip or in a separate chip.

-

2.0 RFFE Master IP

- The MIPI RFFE bus is is 2-wire serial interface which utilizes a bus frequency of up to 26 MHz and timing accurate trigger mechanisms to allow control of timing critical functions.

- It is used to connect a digital RFIC to RF front end components, like Power Amplifiers, Low-Noise Amplifiers and Antenna Sensors, which are considered RFFE Slaves

-

MIPI - Enables high-speed, low-power data transfer for displays and cameras

- MIPI (Mobile Industry Processor Interface) is a high-speed, low-power interface designed for video and imaging applications in mobile and embedded devices. It supports DSI for displays and CSI for cameras, ensuring efficient data transfer and high performance.

- MIPI is widely used across mobile devices, automotive systems, wearables, and more. Its scalability, flexibility, and ability to support high-quality video and imaging make it ideal for various industries, including healthcare, VR/AR, and consumer electronics.

-

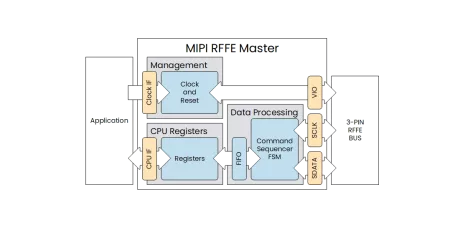

MIPI RFFE Master IP Core

- Fully compliant with MIPI RFFE v3.0 Specification

- Supports all RFFE Slave commands

- Support Standard, Timed and Mappable Triggers

-

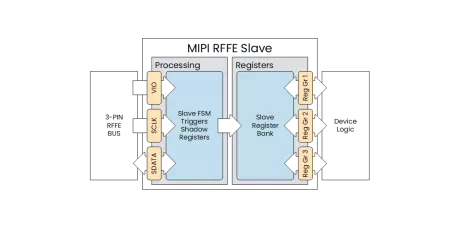

MIPI RFFE Slave IP Core

- Fully compliant with MIPI RFFE v3.1 Specification

- Supports all RFFE Slave commands

- Support Standard, Timed and Mappable Triggers

- Supports all USID Prgramming procedures: 1, 2 and 3

-

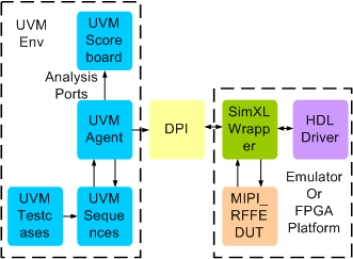

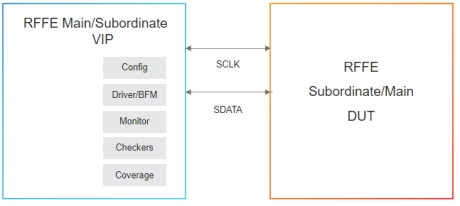

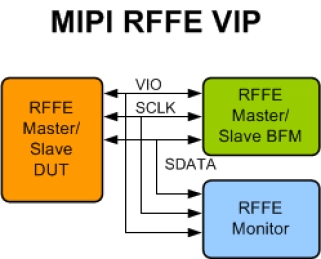

Simulation VIP for MIPI RFFE

- Topology

- Multiple subordinate and multiple main devices topology

- Packet Generation

- Command, Address, Data, and No Response Frame generation

-

MIPI RFFE Verification IP

- Supports 1.0,2.0,2.1 and 3.0 MIPI RFFE Specification.

- Full MIPI RFFE Master and Slave functionality.

- Operates as a Master, Slave, or both.

- Monitor, Detects and notifies the testbench of all protocol and timing errors.

-

MIPI RFFE Synthesizable Transactor

- Supports 1.0,2.0 and 2.1 MIPI RFFE Specifications

- Supports Full MIPI RFFE Master and Slave functionality

- Operates as a Master, Slave, or both

- Supports all topologies as per the MIPI RFFE specification