MIPI Controller IP

MIPI Controller IP cores manage the flow of data between processors and peripherals, ensuring seamless integration and low-power operation. MIPI Controller IP supports a wide range of MIPI interfaces, such as MIPI CSI-2 IP for camera modules, MIPI DSI IP for display applications, and MIPI UFS IP for storage solutions. Additionally, other MIPI interfaces like MIPI I3C IP, MIPI SLIMbus IP, and MIPI SoundWire IP offer flexible solutions for sensor, audio, and bus communication.

All offers in

MIPI Controller IP

Filter

Compare

282

MIPI Controller IP

from

38

vendors

(1

-

10)

-

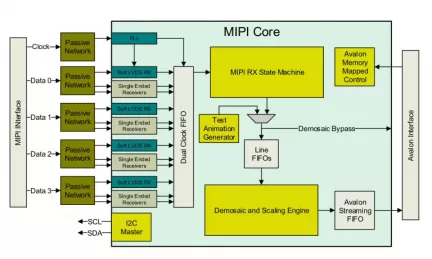

MIPI CSI2 Receiver

- Provides Compatible MIPI D-Phy v1.1 physical layer using FPGA LVDS/LVCMOS IO and passive network

- Supports CSI-2 protocol for unidirectional data transfer

- Compatible with D-PHY Configured for 1 clock and 4 data lanes

- Intended for per-lane clocks rates up to 1 Gbps, depending on device speed grade

-

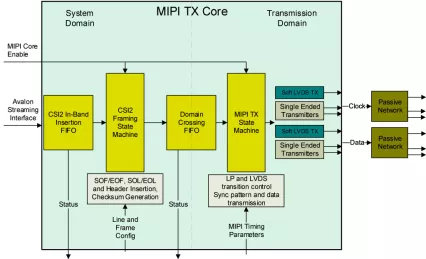

MIPI CSI2 Transceiver

- Provides Compatible MIPI D-Phy v1.1 physical layer using FPGA LVDS/LVCMOS IO and passive network

- Supports CSI-2 protocol for unidirectional data transfer

- Compatible with D-PHY Configured for 1 clock and 1 data lane

- Intended for per-lane clocks rates up to 1 Gbps, depending on device speed grade

-

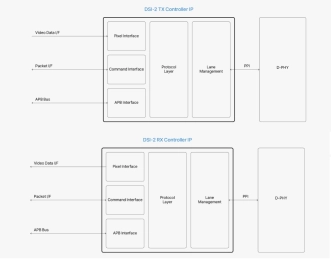

DSI-2 TX/RX Controller

- DSI-2 TX/RX IP supports both transmit and receive functions in line with the DSI-2 v1.1 and D-PHY v2.0 standards.

- Designed for modern SoCs integrating display functionality, it supports high-speed and low-power modes, lane configurability, and robust link features—making it ideal for advanced embedded display applications.

-

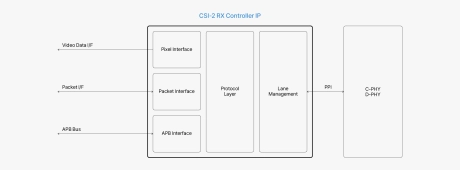

MIPI CSI-2 RX Controller

- Lane merging, virtual channel detection, and programmable data extraction

- Error detection and correction, including packet-level and protocol decoding errors

- Supports all pixel formats defined in the CSI-2 standard

-

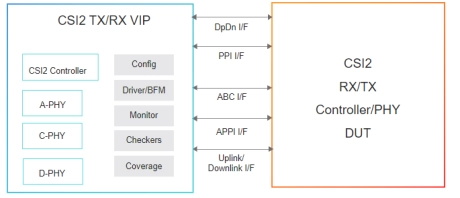

Simulation VIP for MIPI CSI-2

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection at CSI-2, D-PHY, C-PHY and A-PHY levels

- Callbacks access at multiple TX and RX queue points for scoreboarding and data manipulation

-

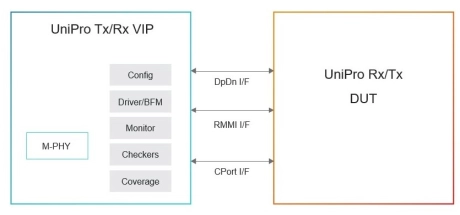

Simulation VIP for MIPI UniPro

- Compliance: Contains predefined checks to verify that the DUT agents adhere to the protocol rules

- Error detection: Supports error detection on all layers, more than 240 different protocol checks

- Coverage: Monitors, checks, and collects coverage on bus traffic using hundreds of automatic protocol checks, including configuration and runtime checks

-

MIPI SoundWire I3S Manager IP

- The MIPI SoundWire I3S Manager IP enables efficient, low-power, and high-fidelity audio data transfer for mobile, consumer, and automotive applications.

- Compliant with the MIPI SoundWire I3S (Inter-IC Sound) standards, it supports synchronized, multi-channel audio over a scalable two-wire interface, ideal for connecting digital microphones, amplifiers, and codecs in space-constrained designs.

-

MIPI SoundWire I3S Peripheral IP

- The MIPI SoundWire I3S Peripheral IP delivers seamless, low-power, and high-quality audio connectivity for a range of mobile, consumer, and automotive devices.

- Fully compliant with the MIPI SoundWire I3S (Inter-IC Sound) specifications, it enables synchronized, multi-channel audio communication with a compact and efficient two-wire interface, ideal for integrating digital microphones, amplifiers, or audio codecs.

-

MIPI SoundWire I3S Verification IP

- Full MIPI SoundWire I3S Master, Slave and Monitor functionality

- Supports MIPI Soundwire-I3S Bus Draft Specification v0.4r06.

- Supports system with one master and one or more slaves (upto 8 slaves).

- Supports LVDS PHY for higher speed and a single-ended CMOS PHY for lower speed systems.

-

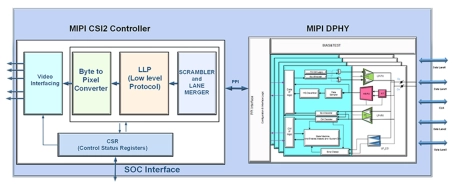

MIPI CSI2 Interface Solution

- Brite provides full solution for the MIPI CSI interface, which receives the data from sensors in PHY layer, and then converts the byte data to pixel after lane data mergence.

- Data scramble is an optional feature to decrease the EMI effect.

- A standard PPI interface is implemented for the connection between MIPI PHY and CSI controller. Brite MIPI CSI interface solution supports image applications with varying pixel formats.