PCI IP for UMC

Welcome to the ultimate

PCI IP

for

UMC

hub! Explore our vast directory of

PCI IP

for

UMC

All offers in

PCI IP

for

UMC

Filter

Compare

22

PCI IP

for

UMC

from

7

vendors

(1

-

10)

-

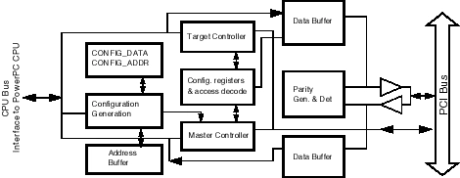

PowerPC to PCI Bridge

- Fully supports PCI specification 2.1 and 2.2 protocol.

- Designed for ASIC and PLD implementations.

- Fully static design with edge triggered flip-flops.

- Supports all PowerPC CPU with 603 bus interface and MPC860 interface.

-

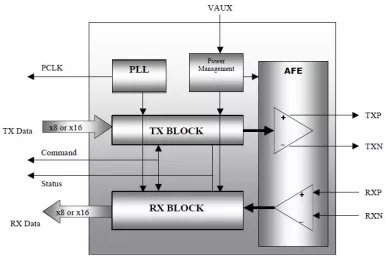

PCI Express PIPE PHY Transceiver

- Supports 2.5Gb/s serial data rate

- Utilizes 8-bit or 16-bit parallel interface to transmit and receive PCI Express data

- Full Support for Auxiliary Power (Vaux) for Energy aware systems like Multi-Port Host Controllers

- Data and clock recovery from serial stream on the PCI Express bus

-

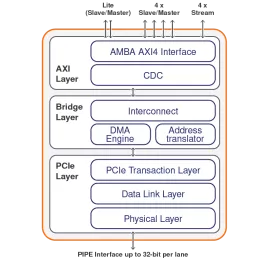

PCIe 3.1 Controller with AXI

- Compliant with the PCI Express 3.1/3.0, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 8 GT/s, 5 GT/s, 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.

-

PCIe 2.0 PHY, UMC 40LP, x1

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, UMC 40LP x4, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, UMC 40LP x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, UMC 28HPC+ x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, UMC 28HPC+ x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 3.0 PHY in UMC (12nm)

- Physical coding sublayer (PCS) block with PIPE interface

- Supports PCIe 3.1, 2.1, 1.1 encoding, backchannel initialization

- Spread-spectrum clocking (SRIS)

- Supports PCIe power management features, including L1 substate; power gating and power island; DFE bypass option and voltage mode Tx with under drive supply options

-

PCIe 2.1 PHY(12nm,14nm, 16nm, 28nm, 40nm, 55nm)

- Fully compliant with PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#