I/O Library IP for TSMC

Welcome to the ultimate

I/O Library IP

for

TSMC

hub! Explore our vast directory of

I/O Library IP

for

TSMC

All offers in

I/O Library IP

for

TSMC

Filter

Compare

16

I/O Library IP

for

TSMC

from

4

vendors

(1

-

10)

Filter:

- 6nm

-

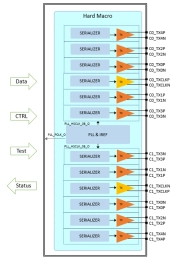

LVDS / sub-LVDS / DPHY TX - TSMC 6FFC

- The LVDS/Sub-LVDS/DPHY Combo TX converts parallel RGB data and 7/8/10 bits of CMOS parallel data into serial data streams.

- A phase-locked clock is transmitted in parallel with the data streams over a dedicated high-speed link.

- The polarity of differential signals for each data lane can be controlled.

-

I/O Library

- Dolphin Technology offers an extensive array of Interface IP, all of whichhasbeen optimized for ultra high performance across all processes supported.

- Our I/O portfolio includes: Standard I/O (General Purpose I/O or GPIO), Specialty I/O (bus-specific I/O), NAND Flash I/O and DDRx & LPDDRx I/O.

-

TSMC N6 1.8V/3.3V Fail-Safe Fail-Tolerant SMBus

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N6 1.2V/1.8V/2.5V/3.3V Fail-safe GPIO

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N6 1.2V/1.8V/2.5V/3.3V GPIO

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N6 1.8V/2.5V/3.3V GPIO

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N6 1.8V/2.5V/3.3V I3C IO

- Synopsys I3C IO library supports a simplified system of connecting and managing multiple sensors in a device

- Multiple sensor secondary devices can be controlled by one I3C primary device at a time

- It offers backward compatibility with I2C legacy devices, is designed for high IO voltage domains and supports low-core voltage domains

- The I3C incorporates the Schmitt-Trigger function, supports I2C Legacy Fast Mode and FM+ Mode, and includes HBM and CDM ESD protection

-

TSMC N6 3.3V SMBus (I2C)

- Synopsys Inter-Integrated Circuit (I2C) IO library is used for two wire interfaces to connect low-speed devices like EEPROM, A/D, and D/A converters and microcontrollers on the same bus

- It is designed for higher IO voltage supply with support for low core voltage and includes fail-safe and fail-tolerance options

- The following operating modes are supported: * Standard Mode: 100 kHz * Fast Mode: 400 kHz * Fast-Plus Mode: 1 MHz * High-Speed Mode: 3.4 MHz

-

TSMC N6 1.8V LVDS IO with CDM 7A

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V

-

BaseKit contains supply cells, power management cells, ring building cells, other common cells for TSMC N6 3.3V IO