General Purpose PLL IP for TSMC

Welcome to the ultimate

General Purpose PLL IP

for

TSMC

hub! Explore our vast directory of

General Purpose PLL IP

for

TSMC

All offers in

General Purpose PLL IP

for

TSMC

Filter

Compare

20

General Purpose PLL IP

for

TSMC

from

5

vendors

(1

-

10)

Filter:

- 16nm

-

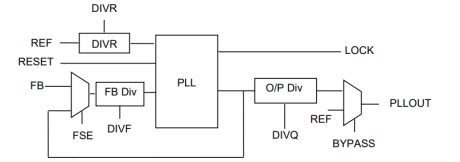

Wide Range Programmable Integer PLL on TSMC CLN16FFC

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Fully integrated inside customer-specified IO ring

-

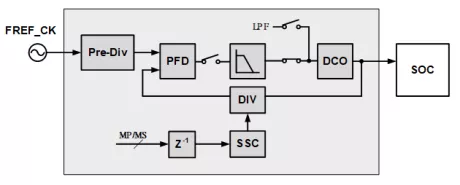

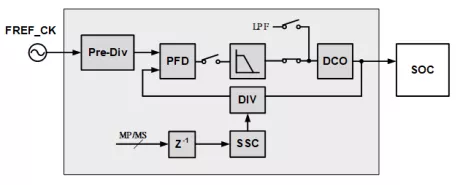

3GHz, low jitter fractional-N, Digital PLL, TSMC 16FFC, N/S orientation

- Pure core voltage design

- Compact IP size (< 0.013mm²) and low power consumption (1.1mW @ 3GHz)

- Compatible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter (< ±15%/V)

-

4.8GHz low jitter fractional-N, Digital PLL, TSMC 16FFC, N/S orientation

- Pure core voltage design

- Compact IP size (< 0.013mm²) and low power consumption (1.1mW @ 3GHz)

- Compatible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter (< ±15%/V)

-

Ultra-Low Power Fractional PLL IP in in TSMC (12/16nm FFC, 22nm ULP/ULL, 28nm HPC+)

- Supports wide input frequency range: 10MHz to 240MHz

- Supports 3:1 output frequency range allows optimization for power and jitter performance

- 24-bit fractional accuracy

- Supports Spread Spectrum Clocking

-

Low Power Fractional PLL IP in TSMC(12/16nm FFC, 22nm ULP/ULL, 28nm HPC+)

- Compact IP size ( smaller than 0.01mm²) and low power consumption ( < 2.7mW @ 3.5GHz )

- Compactible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter ( < +-15ps )

- Support 24-bit fractional accuracy

-

14GHz Integer-N High-Speed PLL

- Type II hybrid Integer-N LC-PLL

- Quadrature clocks at 14GHz and 7GHz

- Fast locking

-

PCIe Gen3 Class SSCG PLL on TSMC CLN16FFC

- High performance design emphasis for meeting low jitter requirements in PCI Express applications

- Implemented with Analog Bits’ proprietary architecture

- Low power consumption

- Spread Spectrum Clock Generation (SSCG) and tracking capability

-

Aeonic Generate Clock Generation Module [PLL], 8x smaller than fractional analog solutions

- Process portable

- Proven (65nm to 3nm)

- Full SCAN testable

- Core voltage supply

-

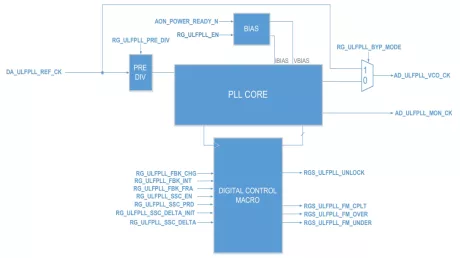

TSMC CLN16FF+LLLVT 16nm Ultra PLL - 15MHz-3000MHz

- New state-of-the-art architecture using high-speed digital and analog circuits that offers unprecedented operating ranges and extremely high performance.

- Ultra low jitter performance for the most demanding SerDes and ADC reference clocks.

- Ultra wide frequency range with multiplication factors over 250,000 to support 32KHz to 1GHz references.

- Precise frequency control with a least 26 fractional bits (at least 10 precise) for extremely high fractional-N resolution.

-

TSMC CLN16FF+LLLVT 16nm General Purpose PLL - 600MHz-3000MHz

- Designed as a wide range clock multiplier with deskew capability.

- Delivers optimal jitter performance over all multiplication settings.

- Low area and low power.

- Suitable for system clock, DDR and general purpose applications.