Analog IP for TSMC

Welcome to the ultimate

Analog IP

for

TSMC

hub! Explore our vast directory of

Analog IP

for

TSMC

All offers in

Analog IP

for

TSMC

Filter

Compare

76

Analog IP

for

TSMC

from

9

vendors

(1

-

10)

Filter:

- 6nm

-

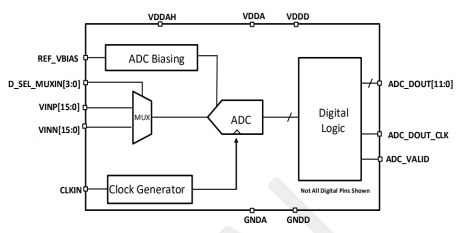

12-bit, 5 MSPS ADC with 8:1 Input Mux in a TSMC 6nm

- The ODT-ADS-12B5M-6T is an ultra-low-power, high-linearity ADC with rail-to-rail inputs designed in a TSMC 6nm process.

- This 12-bit, 5MSPS ADC supports input signals up to 1 MHz and features excellent static and dynamic performance.

- The input front-end includes a mux that can support 16 single-ended or differential inputs.

-

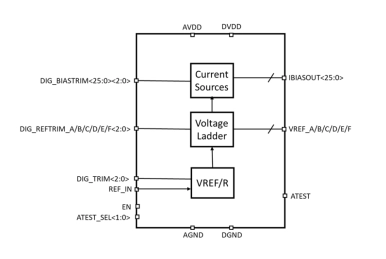

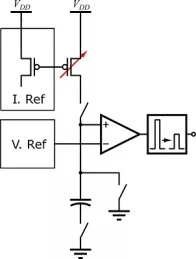

Voltage & Current Reference Generator in TSMC 6/7nm FFC

- The ODT-REF-6T is a reference current and voltage generator. This block includes a VREF/R circuit to create programmable voltages and currents.

- ODT-REF-6T requires a constant 0.6V voltage input (ideally derived from a bandgap) in order to generate the required signals.

-

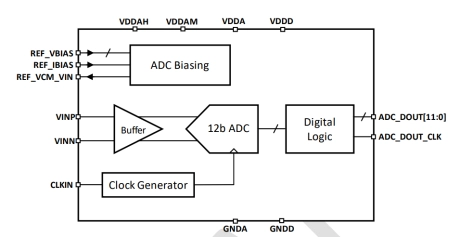

12 bit 250MSPS ADC on TSMC 7nm

- The ODT-ADS-12B250M-7T is an ultra-low power ADC designed in a 7nm CMOS process.

- This 12-bit, 250MSPS ADC supports input signals up to 100MHz and features a differential full-scale range of 0.8Vpp and excellent static and dynamic performance.

-

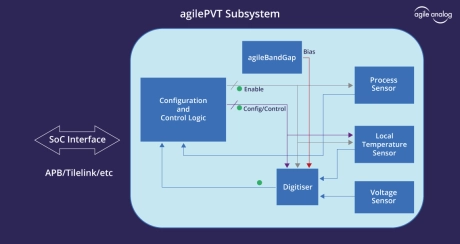

PVT Sensor Subsystem

- Start-up time: Typ 20us

- Current consumption: Max 25uA

- Industry standard digital interface

- Fully integrated macro

- Standard AMBA APB interface

-

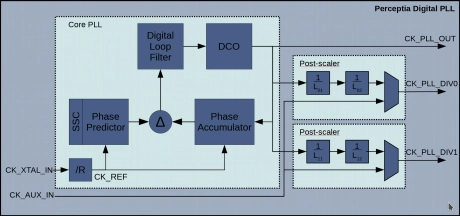

All Digital Fractional-N RF Frequency Synthesizer PLL in TSMC N6/N7

- Fractional Multiplication with frequencies up to 8GHz

- Extremely low jitter (sub 300fs RMS)

- Small size (< 0.05 sq mm)

- Low Power (< 7mW)

-

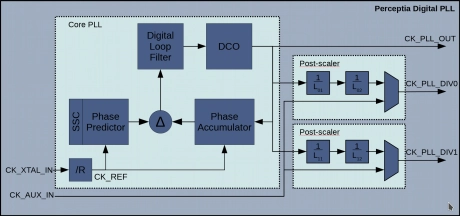

Low Power All Digital Fractional-N PLL in TSMC N6/N7

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

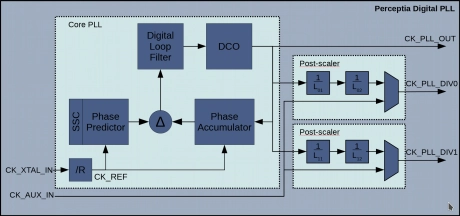

Low Power All Digital Fractional-N PLL in Samsung 8LPP

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

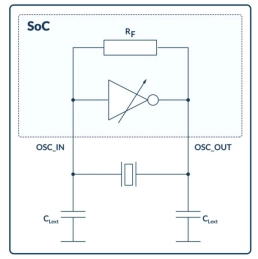

Crystal Oscillators

- The crystal oscillator macros are available in a wide range of industry-standard quartz crystals and MEMS resonators operating in the fundamental mode in the 32 kHz to 80 MHz range.

- These oscillators, which are both power and area efficient, have a programmable transconductance to allow users to find the optimal balance between jitter and power consumption.

-

Free running oscillators

- Compact and low power

- No external components

- Baseline CMOS logic process masks only

- Excellent frequency precision over PVT after trimming

-

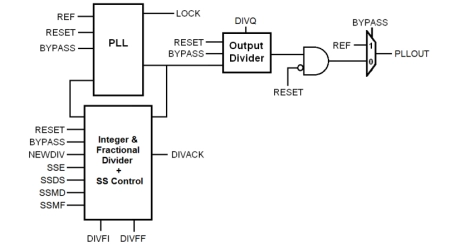

Low Power FracN/SSCG PLL on TSMC CLN6FF

- Electrically Programmable PLL with Fractional-N divide and Spread Spectrum Clock Generation

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Very fine precision: near 1 part per billion resolution

- Fully integrated 32-bit datapath (8-bit integer plus 24-bit fractional)