Peripheral IP for SMIC

Welcome to the ultimate

Peripheral IP

for

SMIC

hub! Explore our vast directory of

Peripheral IP

for

SMIC

All offers in

Peripheral IP

for

SMIC

Filter

Compare

8

Peripheral IP

for

SMIC

from

4

vendors

(1

-

8)

-

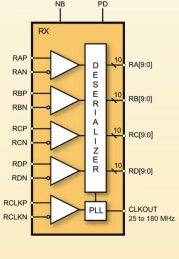

LVDS Deserializer IP

- The MXL-DS-LVDS is a high performance 4-channel LVDS Deserializer implemented using digital CMOS technology.

- Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 10 bits wide per channel. The input clock is 25MHz to 165MHz. The De-serializer is highly integrated and requires no external components.

-

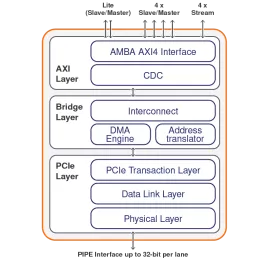

PCIe 3.1 Controller with AXI

- Compliant with the PCI Express 3.1/3.0, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 8 GT/s, 5 GT/s, 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.

-

Camera 6/7-mode Combo Receiver - 1G/1.5Gbps

- The CL12684KM4-8-12-16R3AM6-7ZIP is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to Host System.

- The CL12684KM4-8-12-16R3AM6-7ZIP is designed to support data rate in excess of maximum 1Gbps utilizing sub-LVDS / mini-LVDS / LVDS / HiSPi(SLVS-400, HiVCM) / MIPI-DPHY / CMOS-1.8V / CMOS-3.3V interface specification.

-

Dual FPD-link, 30-Bits Color LVDS Receiver, 170Mhz (SVGA/FHD@120Hz) LVDS de-serializer 10:70 channel decompression with automatic de-skew

- Layout structure based on 0.13um Logic 1P6M, 1P7M, or 1P8M Salicide 1.2V/3.3V process.

- 1.2V/3.3V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3- 1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 11.9Gbps bandwidth (40 to 170Mhz pixel clock) per pixel channel (Full HD @ 120Hz)

-

Dual RSDS Transmitter, 30-bit color, 40-300Mb/s (SVGA/UXGA/full HDTV) LCD & Plasma display

- • 20 to 150 Mhz Pixel rate per channel ( 40 to 300 Mb/s SDR input, 40 to 300 Mb/s DDR output )

- • 30 DATA + 9 RSDS CLK channels

- • Complies with RSDS “Intra-Panel” Interface Specification rev1.0, May 2003.

- • 1P6M layout structure based on 0.18um 1P6M generic logic process.

-

Dual RSDS Transmitter, 24/18-bit color, 40-300Mb/s (SVGA/UXGA/full HDTV) LCD & Plasma display

- • 20 to 150Mhz Pixel rate ( 40 to 300 Mb/s SDR input, 40 to 300 Mb/s DDR output)

- • Complies with RSDS “Intra-Panel” Interface Specification rev1.0, May 2003.

- • 1P6M layout structure based on 0.18um 1P6M generic logic process.

- • 3.3V/1.8V 10% supply voltage, -40/+125C

-

LVDS Transmitter 1250Mb/s, 800Mhz clock with RSDS support

- • 1P6M layout structure based on 0.18um 1P6M 1.8V

- generic logic process.

- • 3.3V/1.8V ±10% supply voltage, -40/+125°C temperature.

- • IEEE Standard 1596.3-1996 and ANSI/TIA/EIA- 644-A Specifications.

-

Dual RSDS Transmitter, 30-bit color, 80-400Mb/s (SVGA/Full HDTV@120Hz)

- • 40 to 200 Mhz Pixel rate per channel ( 80 to 400 Mb/s SDR input, 80 to 400 Mb/s DDR output)

- • 30 DATA + 9 RSDS CLK channels

- • Complies with RSDS “Intra-Panel” Interface Specification rev1.0, May 2003.

- • 1P6M layout structure based on 0.13um 1P6M generic logic process.