Memory & Libraries IP for SMIC

Welcome to the ultimate

Memory & Libraries IP

for

SMIC

hub! Explore our vast directory of

Memory & Libraries IP

for

SMIC

All offers in

Memory & Libraries IP

for

SMIC

Filter

Compare

525

Memory & Libraries IP

for

SMIC

from

21

vendors

(1

-

10)

-

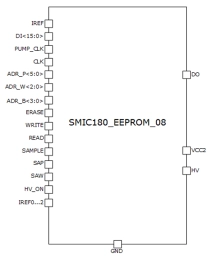

1Kbyte EEPROM IP with configuration 64p8w16bit

- The block is a nonvolatile electrically erasable programmable read-only memory (EEPROM) with volume 1Kbyte (16(bit per word) x 8(words per page) x 64(pages)) with single-bit output data and parallel write data in one word.

- Write EEPROM page data comes to input di<15:0> and write process execute if signal wr=“1”.

-

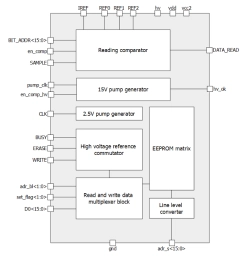

1024-bit EEPROM IP with configuration 32p2w16bit

- The block is a nonvolatile electrically erasable programmable read-only memory (EEPROM) with volume 1024 bits (16(bit per word) x 2(word per page) x 32(page)), which is organized as 32 pages of 2 words by 16 bit with single-bit output data and parallel write data.

- Data writing in EEPROM consists of 2 phases - erasing and writing.

-

512-bit EEPROM IP with configuration 16p2w16bit

- The block is a nonvolatile electrically erasable programmable read-only memory (EEPROM) with volume 512 bits (16(bit per word) x 2(word per page) x 16(page)), which is organized as 16 pages of 2 words by 16 bit with single-bit output data and parallel write data.

- Write EEPROM page data comes to input D0<15:0> and write by words to latch through the signal SAMPLE, while the signal write in a state of «1». The address of a word written down in latches is defined by two low bits of the bus adr_bl<1:0>.

-

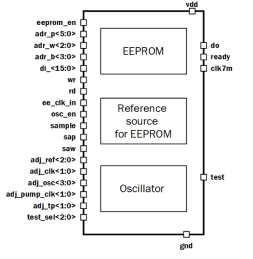

1Kbyte Embedded EEPROM with configuration 64p8w16bit

- SMIC EEPROM CMOS 0.18 um

- 1Kbyte of available memory 16(bit per word) x 8(words per page) x 64(pages) bit

-

Embedded flash IP, 1.5V/5V SMIC 90nmBCD

- Supports high temperature and long retention life time for severe automotive requirement

- Low power in Program/Erase operation for power critical applications

- Requires few (2~3) additional masks

- No change to SPICE model of Standard CMOS process, for re-using existing design and IP

-

Embedded flash IP, 1.32V/3V PSMC 90nm

- Supports high temperature and long retention life time for severe automotive requirement

- Low power in Program/Erase operation for power critical applications

- Requires few (2~3) additional masks

- No change to SPICE model of Standard CMOS process, for re-using existing design and IP

-

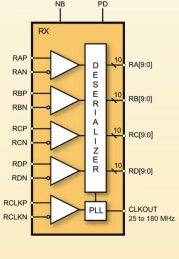

LVDS Deserializer IP

- The MXL-DS-LVDS is a high performance 4-channel LVDS Deserializer implemented using digital CMOS technology.

- Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 10 bits wide per channel. The input clock is 25MHz to 165MHz. The De-serializer is highly integrated and requires no external components.

-

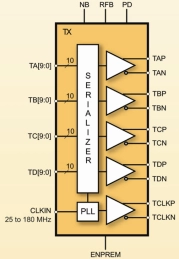

LVDS Serializer IP

- The MXL-SR-LVDS is a high performance 4-channel LVDS Serializer implemented using digital CMOS technology. Both the serial and parallel data are organized into four channels.

- The parallel data width is programmable, and the input clock is 25MHz to 165MHz. The Serializer is highly integrated and requires no external components.

-

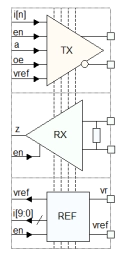

LVDS Transceiver

- Meets or exceeds the TIA/EIA-644 LVDS standard.

- Driver, Receiver, Bias, and Power cells included.

- Greater than 400Mbs data rate.

- 1.8V core voltage, 5V IO voltage.

- Receive fault detection.

- 0.3ns differential pulse skew.

-

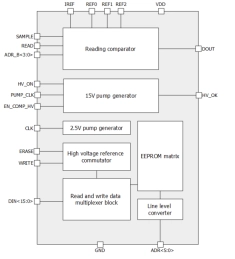

1Kbyte EEPROM with configuration 64p8w16bit

- SMIC EEPROM CMOS 0.18 um

- High density of memory cells

- Writing and erasing data by one high-voltage pulse

- Programming and erase time – 2 ms (determined by specification of the EEPROM SMIC cell)