Memory Controller/PHY IP for Samsung

Welcome to the ultimate

Memory Controller/PHY IP

for

Samsung

hub! Explore our vast directory of

Memory Controller/PHY IP

for

Samsung

All offers in

Memory Controller/PHY IP

for

Samsung

Filter

Compare

41

Memory Controller/PHY IP

for

Samsung

from

5

vendors

(1

-

10)

-

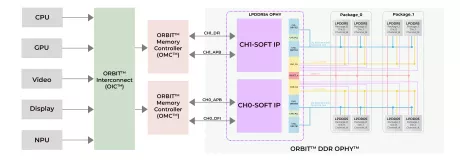

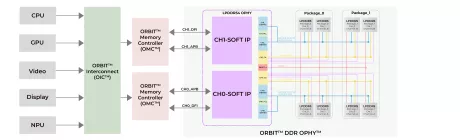

LPDDR5X/5/4X/4 combo PHY at Samsung SF5A

- Compliant for JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- x16 and x32 channel support

-

LPDDR6/5X/5 PHY V2 - SS SF2P

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

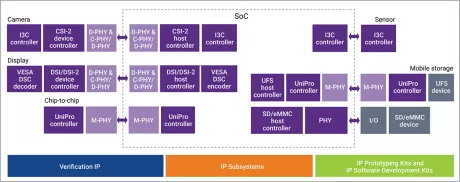

Samsung 8LPU 3.3V SD/eMMC PHY

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

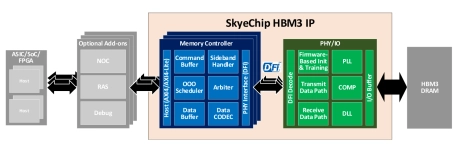

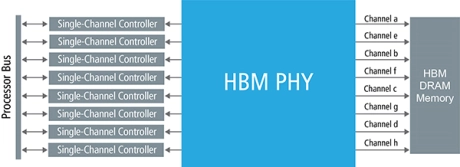

High Bandwidth Memory 3 (HBM3/3E) IP optimized for Samsung SF4X

- The HBM3 IP consists of a PHY and memory controller optimized for Samsung SF4X process to support the HBM3 memory standard (JESD238A) operating at up to 9.6 Gbps/pin.

- The HBM3 IP is designed for high memory throughput and low latency applications while minimizing area and power consumption.

-

LPDDR5/4x/4 PHY IP for Samsung 14LPU

- Compliant with JEDEC standards for LPDDR5/4x/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports 1,2, or 4 ranks

- Multiple frequency states

-

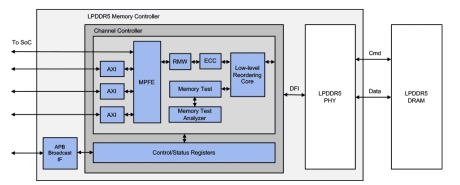

LPDDR5T / LPDDR5X / LPDDR5 Controller

- Support for all LPDDR5T/5X/5 devices

- Bank management logic monitors status of each bank

- Queue-based user interface with reordering scheduler

- Look-ahead activate, precharge, and auto-precharge logic

- Parity protection for all stored control registers

- PHY interface based on DFI 5.1 standard

-

HBM2E/HBM2 PHY

- Advanced clocking architecture minimizes clock jitter

- DFI PHY Independent Mode for initialization and training

- IEEE 1500 interface, Memory BIST feature, and loop-back function

- Designed for optimized interposer routing

- Pin programmable support for lane repair

-

DDR4 multiPHY SP - SS 14LPP

- Support for JEDEC standard DDR4, DDR3, LPDDR2, and LPDDR3 SDRAMs

- Scalable architecture that supports data rates up to DDR4-2667

- Support for DIMMs

- Delivery of product as a hardened mixed-signal macrocell component allows precise control of timing critical delay and skew paths

-

LPDDR4 multiPHY V2 - SS 8LPU

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4 multiPHY V2 - SS 8LPP for Automotive AEC-Q100 Grade 1

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor