Reed-Solomon IP

Welcome to the ultimate Reed-Solomon IP hub! Explore our vast directory of Reed-Solomon IP

All offers in

Reed-Solomon IP

Filter

Compare

43

Reed-Solomon IP

from

20

vendors

(1

-

10)

-

-

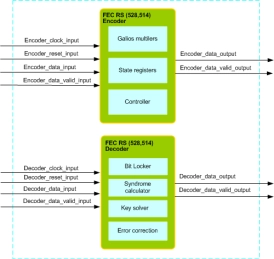

FEC RS (528,514) IIP

- Compliant with CPRI Specification V7.0, IEEE Standard 802.3.2018 Ethernet specification and JESD204D Specification.

- Supports full FEC functionality.

- Supports Reed Solomon (528,514) FEC, 10-bit symbols.

- Supports different input and output data widths of multiples of 10-bits.

-

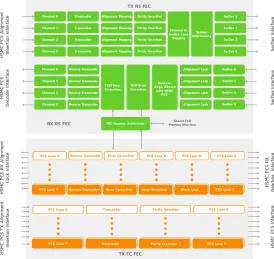

HDMI 2.1 FEC Receiver (Tx)

- HDMI 2.1 compliant

- Reed-Solomon RS (255,251) FEC, 8-bit symbols

- Supports 3-lane and 4-lane operation

- Error counters included (Rx only)

-

HDMI 2.1 FEC Transmitter (Tx)

- HDMI 2.1 compliant

- Reed-Solomon RS (255,251) FEC, 8-bit symbols

- Supports 3-lane and 4-lane operation

- Error counters included (Rx only)

-

FEC RS (198,194) IIP

- Supports the Universal Serial Bus 4 Specification and VESA Display Port version 2.0/2.1 Specification.

- Supports full FEC functionality.

- Supports Reed Solomon (198,194) FEC, 8-bit symbols.

- Supports the input and output data widths of multiples of 8-bit.

-

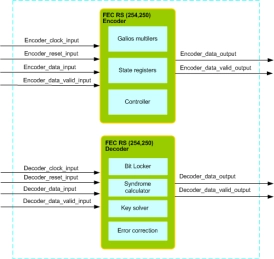

FEC RS (254,250) IIP

- VESA Display Port version 1.4/2.0/2.1 compliant.

- Supports full FEC functionality.

- Supports Reed Solomon (254,250) FEC, 10-bit symbols.

- Supports the input and output data widths of multiples of 10-bit.

-

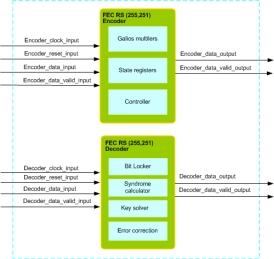

FEC RS (255,251) IIP

- HDMI specification 2.1/2.1a and Scalabale Low Voltage Signaling with Embedded Clock (SLVS_EC) compliant.

- Supports full FEC functionality.

- Supports Reed Solomon (255,251) FEC, 8-bit symbols.

- Supports the input and output data widths of multiples of 8-bit.

-

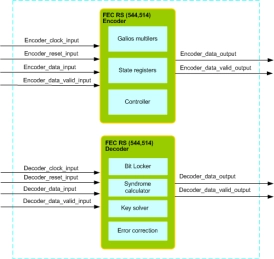

FEC RS (544,514) IIP

- Compliant with CPRI Specification V7.0, IEEE Standard 802.3.2018 Ethernet specification and JESD204D Specification.

- Supports full FEC functionality.

- Supports Reed Solomon (544,514) FEC, 10-bit symbols.

- Supports different input and output data widths of multiples of 10-bits.

-

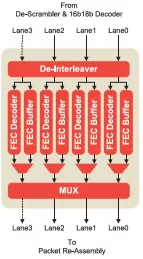

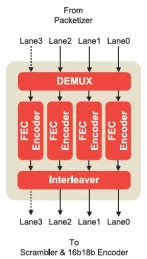

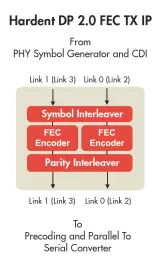

VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- VESA DisplayPort 1.4 compliant

- Reed-Solomon RS (254,250) FEC, 10-bit symbols

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode requires 2 FEC IP core instances)

- DisplayPort main 8b/10b encoder included (Tx only)

- Status and control can be done with signals or optionally via an integrated APB register module (Rx)

-

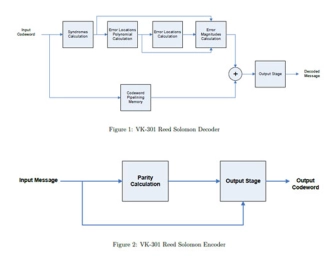

Reed Solomon

- High performance Reed Solomon IP Core (Encoder and Decoder).

- Supports error and erasure decoding.

- Parameterized codeword length.

- Code generator polynomial: (x + λ^0 )(x + λ^1 )(x + λ^2 )...(x + λ^15 ).