Why Hardware Monitoring Needs Infrastructure, Not Just Sensors

Sensors aren't enough: discover the proteanTecs hardware monitoring system.

Chipmakers need comprehensive hardware monitoring, with monitors (Agents) and sensors distributed throughout their devices, to manage the growing complexity and scale of modern SoCs. As designs now incorporate billions of transistors, multiple power and clock domains, and advanced process technologies, traditional characterization, test, and guard-banding approaches no longer provide sufficient visibility or control. Continuous monitoring is becoming the de-facto standard for ensuring performance, quality, reliability, and power efficiency at scale, during both production and in-field operation.

But monitors and sensors alone are not enough. They require infrastructure.

Why Hardware Monitoring Infrastructure Matters

Without infrastructure to orchestrate data collection, process measurements in hardware, provide unified control, enable real-time events, and manage the complete monitoring flow, chipmakers face integration challenges, including:

- Manual orchestration of diverse monitor and sensor types across the chip

- Separate solutions for test and field deployment

- Custom integration work for each new monitoring capability

- Lack of a unified control framework

- Huge data-set read outs

- Inability to use the data in hardware for real-time reaction

These challenges lead to extended development cycles, increased risk, and monitoring solutions that never deliver full value because the infrastructure can't support them.

proteanTecs HW Monitoring Infrastructure: A Smart Control Architecture

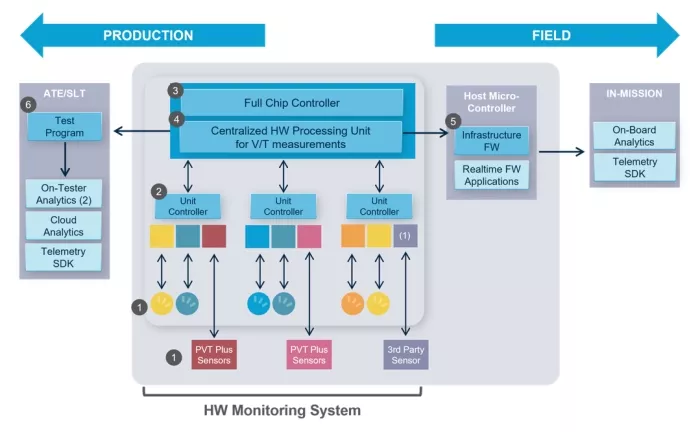

proteanTecs HW monitoring infrastructure connects Agents and sensors to both test equipment and in-field software through a unified control architecture. On-chip monitoring is enabled at production test and mission-mode operation through a single, reusable infrastructure.

From Agents to analytics: proteanTecs connects on-chip monitoring to both production test and in-field operation through a unified infrastructure.

The monitoring architecture delivers all layers required for a complete hardware monitoring system:

- Agents and Sensors (Layer 1)

Provide continuous measurements with high coverage and fine-grained resolution across critical parameters such as timing margin, voltage, temperature, process, and workload. The architecture also supports integration of third-party sensors. - Unit and Local Controllers (Layer 2)

Continuously sample associated Agents, perform local data processing and statistical analysis, generate real-time alerts, and store statistics. Unit Controllers aggregate data and connect monitoring outputs to the chip level. - Full Chip Controller (Layer 3)

Connects to standard test and functional interfaces and virtualizes the hardware monitoring system at the full-chip level. - Centralized Processing Unit for V/T Measurements - Optional (Layer 4)

Collects data to a centralized location, translates Voltage & Temperature measurements into physical values, stores max-min indications and provides over-temperature and catastrophic-temperature HW digital alerts. - Infrastructure Firmware (Layer 5)

Enables real-time, in-field monitoring by handling configuration, operation, data readout, and interrupts. - Test Program (Layer 6)

Enables on-tester and cloud analytics during production test - managing configuration, operation, and data collection.

The same monitoring infrastructure (Layers 2-4) is used for both production test and in-field operation. Only the applications above the infrastructure change. Chipmakers integrate monitoring once and deploy it anywhere, anytime.

The proteanTecs HW monitoring infrastructure integrates through standard industry interfaces in both test and functional modes. This allows the monitoring system to connect seamlessly to existing test equipment, firmware, and system software without custom adapters or proprietary hooks, preserving established design and validation flows.

Hardware Processing Reduces Bandwidth and Enables Real-Time Response

The infrastructure processes monitoring data directly in hardware. On-chip controllers perform statistical analysis and generate alerts based on configurable thresholds, without routing raw data to a host processor.

Hardware processing reduces bandwidth by transmitting only relevant statistics and alerts, rather than continuously streaming raw measurements. Alerts trigger immediately when thresholds are crossed, without waiting for software processing cycles. The HW monitoring system operates independently, freeing compute resources for primary workloads.

This embedded intelligence means the system can respond to critical events such as voltage droops, thermal spikes, and timing margin threshold-crossing events - before they cause failures in runtime applications. In production testing, it enables use cases such as identifying marginal dies that pass standard tests but carry reliability risks due to latent defects.

proteanTecs IP: The Mastermind Deep Data Generators

The proteanTecs HW Monitoring System is a rich, turnkey solution that includes the HW monitoring infrastructure and the Agents and Sensors.

proteanTecs Agents are on-chip hardware IP blocks designed to continuously observe and measure a chip’s behavior in real time. Embedded directly into silicon, Agents extract high-resolution parametric data across critical domains such as timing margin, maximum cycle to cycle jitter, local IR drop, lifetime acceleration stress, signal integrity, aging effects, delay and process signature. They extract essential data related to a chip's quality and health, and provide capabilities for real-time power reduction and performance improvements. Actionable insights are provided at every stage, including qualification, characterization, validation, production testing, and in-field operation.

Despite this robust functionality, their design remains highly efficient in terms of area usage, power consumption, and adaptability to specific designs.

Agent effectiveness is a result of their strategic embedding in a design, considering:

- Coverage requirements

- Key performance areas

- On-chip variation (number, types, location, configurations)

- Clocks and power domains

- Repetitive areas

- Design architecture and topology

- Specific requirements for application of interest

proteanTecs PVT Sensors provide a fast, accurate, and standardized solution for managing thermal, voltage, and Ldi/dt effects in advanced SoCs. They include Temperature and Voltage sensors, Voltage Droop sensors, and Clock Duty Cycle Distortion sensors. Their primary purpose is to provide real-time visibility into the chip’s operational environment, enabling early detection of potential issues. Designed for advanced process nodes, including Gate-All-Around (GAA) and Backside Power (BSP) technologies, the solution scales across the chip - enhancing power, performance, and thermal management with proven, production-ready value.

proteanTecs categories of Agents and Sensors.

A typical SoC design will have different types of Agents or Sensors, with different configurations and numbers of instantiations, in different areas/blocks. Customers mix and match these configurations based on specific requirements while the monitoring infrastructure remains the same.

Automatic Generation of HW Monitoring System & Collaterals

The proteanTecs EDA tools automatically generate a full implementation-ready HW Monitoring System, including the HW Monitoring Infrastructure and the Agents & Sensors:

- Monitoring unit with:

- Unit controller

- Local controllers per Agent/Sensor family

- Agents and Sensors

- Full-chip controller (main controller of the HW Monitoring System)

- Centralized HW processing unit for voltage and temperature

- Hardened IP collaterals

- Logic integration and verification collaterals

- Implementation and DFT collateral

- Post-silicon tests

- Infrastructure firmware

Integration into chip design requires minimal effort. The proteanTecs EDA flow includes a compiler that automatically generates the HW Monitoring System, producing implementation-ready hardware, firmware, and verification collateral. It uses a small number of top-level interface signals at low frequency and operates without consuming internal memory resources. It delivers a complete, verified monitoring system rather than IP blocks that require extensive custom integration. The system integrates cleanly at both block and full-chip levels, allowing teams to deploy monitoring incrementally or across the entire design.

proteanTecs HW Monitoring System integration and implementation remain agnostic to EDA vendor tooling.

One System, End-to-End Lifecycle Monitoring

Chipmakers implementing hardware monitoring face a fundamental choice: assemble the infrastructure themselves or deploy a complete system.

proteanTecs delivers that complete system - proven in over 150 designs, across multiple foundries and process nodes, down to 2nm. Five integrated layers connect on-chip monitoring to production test and field operation, providing everything needed from data collection through insights without custom development.

The system introduces a complete, silicon-proven platform, not a collection of partial components. It eliminates customer-built logic and missing pieces by providing a single infrastructure that supports both test and mission-mode operation. Hardware processing is built in, enabling scalable monitoring across the entire chip while minimizing bandwidth and integration effort. The system is automatically compiled with the required firmware, interfaces, and verification collateral, making it ready to deploy. Integration requires only a small number of low-frequency interface signals, minimizing routing impact and simplifying physical implementation.

Built from embedded and hardened building blocks within a configurable architecture, the hardware monitoring system scales and adapts to each design while remaining robust and reliable.

It gives chipmakers a faster, lower-risk path to deploying hardware monitoring that delivers real value from silicon bring-up through lifetime operation.

Want to learn how proteanTecs delivers complete monitoring infrastructure and eliminates the work and risk of piecing together partial solutions? Contact us here.

Related Semiconductor IP

- Voltage and Temperature Sensor with integrated ADC - GlobalFoundries® 22FDX®

- 8MHz / 40MHz Pierce Oscillator - X-FAB XT018-0.18µm

- UCIe RX Interface

- Very Low Latency BCH Codec

- 5G-NTN Modem IP for Satellite User Terminals

Related Blogs

- AIoT. Why it's not just another tech buzzword.

- Why Hardware Security Is Just as Critical as Software Security in Modern Systems

- New Product Execution - It's Just not Good Enough

- The Zynq Virtual Platform: Not Just for Pre-Silicon

Latest Blogs

- Why Hardware Monitoring Needs Infrastructure, Not Just Sensors

- Why Post-Quantum Cryptography Doesn’t Replace Classical Cryptography

- The Silent Guardian of AI Compute - PUFrt Unifies Hardware Security and Memory Repair to Build the Trust Foundation for AI Factories

- Heterogeneous NPU Data Movement Tax: Intel's Own Slides Tell the Story

- PQMicroLib-Core now supports PSA Certified Crypto API