How RISC-V Enables Low-Power Vision for ADAS System

As the automotive industry is emerging with Software-Defined Vehicles (SDVs) and autonomous vehicles, Advanced Driver Assistance Systems (ADAS) are encountering serious challenges day by day.

Challenges like high-resolution 360° cameras generating over 30 Gbps of data, which requires real-time processing. Unfortunately, electric vehicles are restricted to a 5W power limit on edge vision/sensor ECUs to enhance their range and manage thermal headroom, making sustained real-time processing a challenge. Proprietary Instruction Set Architectures (ISAs) such as ARM encounter thermal throttling, vendor lock-in, and inefficiencies in sensor fusion, security, and compliance, causing synchronization delays among radar, lidar, and cameras, which puts safety at risk.

Transitioning to a customized, open ISA core like RISC-V helps overcome these obstacles in low-power vision for ADAS. This license-free architecture enables engineers to create specialized, backward-compatible cores optimized for INT8/FP16 convolutions through RVV extensions.

These developments support efficient algorithm stacks that integrate sensors from different vendors with hardware-accelerated timestamp alignment and field-of-view stitching.

RISC-V also enables flexible workload distribution, minimal preprocessing at zonal cameras, and extensive processing by central controllers, while meeting ISO 26262 ASIL-D standards and supporting long lifecycles with secure OTA updates, making ADAS efficient for future mobility.

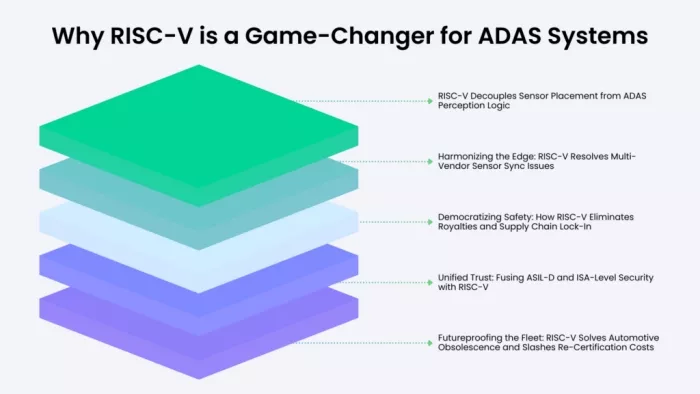

Why RISC-V is a Game-Changer for ADAS Systems

Traditional ADAS systems are struggling to keep up with the massive 30Gbps of data coming from sensors. This is made worse by high power needs and being stuck with specific vendors. RISC-V solves these problems by providing an open and customizable instruction set architecture (ISA). This allows OEMs to build vision pipelines that work independently of any specific sensor.

1. RISC-V Decouples Sensor Placement from ADAS Perception Logic

RISC-V helps us tackle those tricky problems with where to put sensors. Instead of being stuck with rigid, locked-down hardware that only works one way, RISC-V offers a flexible and open design. This means it can change and adapt to fit whatever physical design constraints we’re working with.

Resolving the Design-Perception Conflict

RISC-V smooths things over right at the hardware level, bridging the gap between how we design something and how it needs to function in the real world.

- Engineers can use custom ISA extensions to create specific instructions that deal with “distorted” data immediately. For instance, imagine a radar sensor stuck behind a plastic bumper that weakens its signal. A tiny RISC-V core can run noise-filtering without delay in the hardware to clean up the signal.

- Plus, we can drop these small, power-efficient RISC-V “micro-cores” right where the sensors are. They start processing the data immediately to fix problems, like an airflow blockage, before the bad data even gets to the main central computer (ECU). This lets us make sleeker industrial designs without having to compromise on essential cooling systems.

Escaping the “Re-Certification” Trap

-

Standardized Perception Layers: Unlike proprietary systems that require full re-validation for even minor shifts in sensors, RISC-V features an open Hardware Abstraction Layer (HAL). This adaptability allows the software stack to respond to various placements, which accelerates delta-certification and helps avoid the hefty costs of a $10 million system overhaul.

- On-Chip Auto-Calibration: Custom RISC-V vector processors can carry out real-time geometric correction algorithms. If a sensor’s location is changed for a vehicle redesign, the processor will automatically create a new set of coordinates that reflect the original manufacturer’s safety standards while maintaining compliance with ISO 26262.

- Legacy Component Sustainability: RISC-V’s open ISA will allow the use of reliable legacy components for integration into a vehicle design. If existing sensors’ firmware can be updated to meet new compliance regulations for additional safety features, the overall system can easily be retrofitted using existing hardware. This “backward-compatible safety” approach means legacy components can easily adapt to new system demands. This benefits in reducing expenses.

Overcoming Environmental Blindness

RISC-V facilitates Intelligent Active Maintenance to protect the Operational Design Domain (ODD).

- It features Dedicated Cleaning Controllers, allowing developers to integrate “Maintenance Cores” into the RISC-V SoC for managing active cleaning systems such as ultrasonic nozzles or heaters. These cores keep an eye on sensor clarity and can trigger cleaning cycles without straining the primary AI perception engine.

- Virtual Sensor Reconstruction: Moreover, with the RISC-V Vector (RVV) extension, the system can achieve high-speed “virtual fusion.” If a sensor is obstructed by mud or snow, the RISC-V core can draw on data from surrounding sensors to “fill in” the blind spots in the 3D environmental map, maintaining safety during poor weather.

2. Harmonizing the Edge: RISC-V Resolves Multi-Vendor Sensor Sync Issues

RISC-V helps reduce the 30% “silicon waste” by utilizing specialized instruction sets. One such feature is Custom Data Normalization (ISA Extensions), which allows manufacturers to add custom “fusion-ready” instructions to the RISC-V ISA.

These guidelines can automatically change various data formats, such as converting Radar’s polar coordinates into LiDAR’s Cartesian points, throughout the fetch-execute cycle. This transition from high-level software to low-level hardware can release up to 30% of ECU cycles, enhancing path planning efficiency.

- Vector Acceleration (RVV): With the RISC-V Vector Extension (RVV 1.0), you can process 360° sensor feeds in parallel, which helps normalize data streams from various vendors in real-time, all without the extra burden of individual translation layers.

Overcoming Compliance Barriers (ISO 26262)

RISC-V’s open architecture streamlines the demanding process of obtaining ASIL-D certification.

With Transparent Verification, safety auditors can inspect the precise data path for every sensor input, unlike the opaque “black box” proprietary chips. This clarity makes it easier to confirm that the “worst-case” latency is within acceptable safety limits.

RISC-V Innovation for the Future of ADAS

3. Democratizing Safety: How RISC-V Eliminates Royalties and Supply Chain Lock-In

Many ADAS designs involve proprietary IP cores and licensing fees, which can add a concealed layer of costs that people often refer to as the ‘Hidden Bill of Materials.’

RISC-V offers a solution to this challenge by removing the proprietary barriers that drive up costs for Advanced Driver Assistance Systems (ADAS) and restrict manufacturing flexibility.

Removing Proprietary Lock-in and Royalty Fees

The open-standard design of RISC-V changes the financial landscape for developing ADAS:

- Zero-Royalty Core Logic: Unlike conventional architectures that impose per-chip royalties and hefty annual licensing fees, the RISC-V ISA is available at no cost. This allows OEMs to redirect the savings from royalties towards enhancing sensor hardware or lowering the prices of vehicles.

- Cutting NRE Costs with an Open Ecosystem: By using open-source building blocks and shared verification resources, OEMs can significantly reduce Non-Recurring Engineering (NRE) costs. Engineers can tailor a basic automotive core without the need to pay for a complete proprietary license just to access specific instructions.

Diversifying the Supply Chain (Foundry Agility)

RISC-V offers a flexible architecture that protects OEMs from disruptions in global foundries.

- Architecture Portability: Since RISC-V isn’t linked to a specific silicon vendor, OEMs can create a “Global HAL” (Hardware Abstraction Layer). When a major foundry like TSMC runs into delays, transferring the RISC-V RTL design to another manufacturer, like Intel Foundry Services or GlobalFoundries, can be done with minimal software changes compared to proprietary architectures.

- Multisourcing Readiness: RISC-V allows for a “plug-and-play” method for chips, enabling different vehicle tiers, such as Economy and Luxury, to source chips from various vendors while maintaining the same software stack. This means there’s no need to rewrite safety-critical code for each vehicle model.

Democratizing Safety Features

The adaptability of RISC-V helps OEMs avoid the “feature activation” fees that Tier-1 suppliers typically charge.

- In-House Feature Development: By managing the silicon design, OEMs can add important safety features like Lane Keep Assist and Traffic Sign Recognition as standard hardware functions, freeing them from the obligation to pay external software vendors for each feature.

- Scalable Safety Tiers: Additionally, OEMs can implement the same RISC-V microarchitecture across their entire range of vehicles. They can easily scale the number of active “RISC-V clusters” according to the vehicle’s price point, ensuring that even entry-level models can achieve 5-star NCAP safety ratings without incurring high-tier licensing costs.

4. Unified Trust: Fusing ASIL-D and ISA-Level Security with RISC-V

RISC-V is revolutionizing automotive engineering architecture by fusing security and functional safety into one cohesive silicon design, leaving behind the ineffective “patchwork” solutions of the past.

Integrated Safety: Beyond the “Lockstep” Penalty

With RISC-V, the typical 20% die-area penalty and communication delays associated with conventional safety isolation techniques are outdated.

- Programmable Hardware Enclaves: Instead of adding extra physical microcontrollers, RISC-V supports the creation of Software-Defined Hardware Enclaves. These enclaves leverage custom ISA extensions to provide both spatial and temporal isolation for ASIL-D tasks, all on the same die as high-performance perception tasks.

- Lockstep Cores, which can be configured: Engineers can use RISC-V as an open source, so they will have the ability to design new types of architectures called Flex-lockstep. These cores provide the flexibility to transition between a high-performance mode or operation and a safety-critical lockstep mode and minimise the amount of waste on the silicon and maximise the ability for critical brake function to pass through the congested bus by having dedicated paths (i.e., hardware paths) that can be directly verified.

ISA-Level Root of Trust (The Secure V2X Gateway)

RISC-V’s security enhancements address, which is referred to as the Bolt-On. security problem, where the additional security capabilities are integrated directly into the RISC-V processors’ Instruction Set Architecture (ISA).

- By providing a Native Root-of-Trust (RoT), RISC-V makes it possible to integrate a Secure Monitor (SM) at the ISA level to protect V2X and Infotainment modules from any attack. This method of providing security will allow a compromised module to have no effect on the safety-critical portion of the CAN bus, thus maintaining the security of the vehicle network. The security of the vehicle network is both transparent from a user’s perspective and can be verified via hardware privilege modes.

- Furthermore, RISC-V’s standard Physical Memory Protection (PMP) enables precise control over which software modules can access certain memory regions. This creates a “Zero-Trust” environment within the SoC, preventing any faulty OTA updates from interfering with ADAS perception or steering logic.

Transparent Security Verification

RISC-V’s open architecture provides a distinct advantage when it comes to complying with ISO 26262 and ISO/SAE 21434 (Cybersecurity).

- Eliminating Hidden Backdoors: Unlike proprietary systems, RISC-V’s RTL (Register Transfer Level) is open for security audits. This transparency allows OEMs to mathematically confirm that there are no hidden vulnerabilities or backdoors in the critical safety data path.

- Rapid Security Patching: With an open ISA, the automotive engineering community can swiftly develop and deploy hardware-level security patches (through FPGA-based SoCs or programmable logic) instead of waiting for updates from proprietary vendors.

5. Futureproofing the Fleet: RISC-V Solves Automotive Obsolescence and Slashes Re-Certification Costs

RISC-V addresses the “Silicon Gap” effectively by allowing automotive software to operate independently of hardware lifecycles. This ensures long-term support for many years without the risk of expensive redesigns.

Radical Reduction in Re-Certification Costs

RISC-V is changing the game by eliminating the $10 million re-certification cycle through its innovative “Portable Safety Case.”

- A major benefit is Architecture Continuity: when a proprietary NPU or GPU becomes obsolete, it usually necessitates a full ISO 26262 re-validation due to architectural changes. In contrast, RISC-V maintains a consistent Hardware Abstraction Layer (HAL) across generations. This means that switching from one RISC-V vendor to another is considered a “minor configuration change” rather than a “fundamental redesign,” leading to significant savings in NRE and certification expenses.

- Open-Source Verification Blueprints: In the automotive engineering field, standardized RISC-V verification suites can be utilized. This leads to “Delta Certification,” where the focus is on auditing just the changes from one chip generation to the next, instead of the whole software-hardware stack.

Mitigating Obsolescence via “Silicon Resilience”

RISC-V empowers OEMs to take charge of their hardware future.

By having design ownership of the RTL (Register Transfer Level) for their RISC-V cores, OEMs are no longer dependent on a supplier’s Product Change Notification (PCN). If a particular chip is phased out, the OEM can simply transfer its existing RISC-V design to another foundry.

Looking ahead, the RISC-V architecture is set to lead the way in energy-efficient Advanced Driver Assistance Systems (ADAS) by allowing the creation of highly specialized Systems-on-Chips (SoCs) with custom instruction set extensions. Its modular and open standard characteristics empower designers to fine-tune for power, performance, and area, incorporating dedicated accelerators for AI and machine learning vision applications. This level of design freedom promotes a strong ecosystem for low-power, real-time processing solutions that are crucial for the next generation of autonomous systems.

MosChip delivers advanced Product Engineering solutions for the automotive industry, leveraging RISC-V to enable low-power vision and scalable ADAS architectures for SDVs.

With a strong focus on high-speed protocols and adherence to ISO 26262 standards, MosChip facilitates smooth multi-sensor integration, quick zonal processing, and energy-efficient vision systems. They provide everything from complete SoC design to optimizing edge computing, offering scalable and future-ready silicon solutions that help global Tier-1 suppliers avoid vendor lock-in.

To know more about MosChip’s capabilities, drop us a line, and our team will get back to you.

Related Semiconductor IP

- Compact Embedded RISC-V Processor

- Highly configurable HW PQC acceleration with RISC-V processor for full CPU offload

- Vector-Capable Embedded RISC-V Processor

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

- Enhanced-Processing Embedded RISC-V Processor

Related Blogs

- How PCIe® Technology is Connecting Disaggregated Systems for Generative AI

- MIPS P8700 RISC-V Processor for Advanced Functional Safety Systems

- How to reduce the risk when making the shift to RISC-V

- From ChatGPT to Computer Vision Processing: How Deep-Learning Transformers Are Shaping Our World

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk