Perceptia 基于格芯22FDX工艺的 pPLL08W初期性能测试报告正式发布

2025年10月23日,澳大利亚悉尼

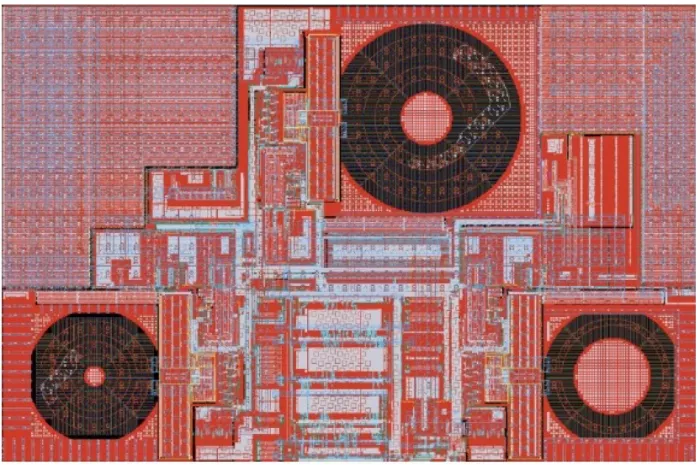

行业领先的低抖动时钟IP供应商Perceptia Devices公司今日宣布,其基于格芯(GlobalFoundries)22FDX工 艺的宽带高性能锁相环pPLL08W的初期性能测试报告现已正式发布。

该报告包含PLL08W锁相环IP在22FDX工艺下的初期测试结果,展现了该款锁相环低相位噪声、低杂散、宽频带 输出与低功耗等优秀特性。此次测试的pPLL08W是Perceptia专为射频应用设计的高性能锁相环IP,特别适用于 无线通信系统,包括 5G 无线通信、WiFi 模块及物联网收发器等应用场景。

“这份初期测试报告可以证明:pPLL08W 在 GF22FDX 平台上展现出了我们预期的射频系统设计所需的优 秀性能与可靠性,”Perceptia Devices 工程副总裁 Tim Robins 表示。“凭借其低抖动和对宽频输出 的支持,以及良好的能耗控制,pPLL08W 将使下一代射频 SoC 在能够满足现代无线标准与实现高速数据 传输同时,达到高能效的要求。”

Perceptia 的 pPLL08W 为市场提供了一款面向射频设计严苛要求的高性能频率合成解决方案。其具备的宽频工 作范围与卓越的相位噪声性能,能够在先进无线系统中实现精准载波生成、高速数据传输及稳定可靠的连接。 此次初期测试数据的发布让有需求的设计团队能够提前了解该款锁相环IP的实际性能表现,从而降低集成风 险并加快射频 SoC 的上市进程。目前Perceptia正进一步推进全面、严格的测试流程。完整的硅片特性测试报告 将在全面测试完成后正式发布。

关于pPLL08W

pPLL08W是一款基于 LC Tank 架构的宽带射频锁相环(PLL)IP核,其输出频率范围覆盖 5.5MHz 至 10.6GHz。pPLL08W专门面向 5G 等需要宽带载波频率的无线与通信应用场景打造,具备优异的相位噪声性能和高 度集成灵活性,助力设计人员在不增加面积或功耗的前提下,构建先进可靠的高性能时序架构。

关于Perceptia Devices

Perceptia Devices 总部位于澳大利亚悉尼,是行业领先的半导体 IP 和设计服务提供商。Perceptia 专注于 高速与超低功耗的混合信号芯片设计,致力于为无线通信、人工智能(AI/ML)、数据转换及混合信号 SoC 等多 领域客户提供时序精准、集成高效的解决方案。凭借深厚的技术积累和灵活的设计能力,Perceptia 在过去20余 年中助力客户加速产品开发,实现卓越性能。

如需了解更多产品信息或索取产品数据手册,您可以通过以下方式联系我们:

Related Semiconductor IP

Related News

- Perceptia Devices 完成 pPLL03 IP 在 GF22FDX 工艺下的硅片特性测 试,报告正式发布

- Perceptia 正式发布基于 GlobalFoundries 22FDX 的 10-bit 极低温 (Cryogenic)数/模(DAC)、模/数(ADC)转换器 IP

- Perceptia 正式发布基于格芯(GlobalFoundries)22FDX 平台的 pPLL05 设计套件

- Perceptia 更新基于格芯(GlobalFoundries)22FDX工艺平台的 pPLL03 设计套件