Perceptia 更新基于格芯(GlobalFoundries)22FDX工艺平台的 pPLL03 设计套件

2025年11月06日,澳大利亚悉尼 -- 行业领先的低抖动时钟IP供应商Perceptia Devices公司今日宣布,正式推出其pPLL03 锁相环IP在格芯 (GlobalFoundries) 22FDX (FD-SOI)工艺节点上的更新版设计套件

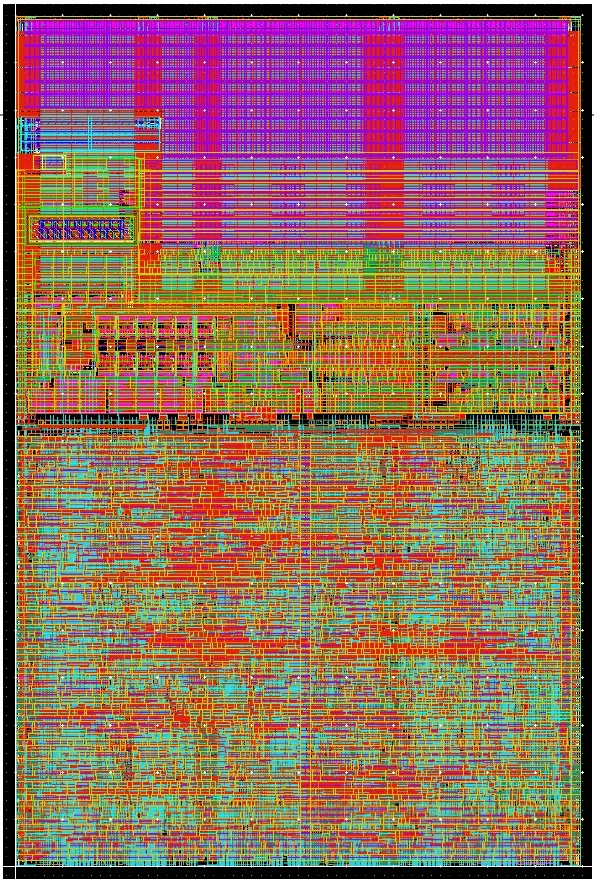

pPLL03是Perceptia推出的低抖动、高性能锁相环IP,专为AI加速器、数模/模数转换器采样时钟以及高速数 字系统等高要求SoC应用优化设计。本次更新的设计套件为SoC开发者提供完整的版图、仿真以及时序收敛支持, 以帮助开发人员实现高效的系统级设计。

此次更新为pPLL03增加了电源管理电路模块,显著提升其对于电源噪声的容忍度,使其在不同的工作环境中具 备更优的可靠性。

pPLL03的关键参数包括:

- 频率输出范围:最高可达4GHz,同时支持整数与分数N分频模式

- 峰值周期抖动:在4GHz输出时小于2.1%周期(约5.25ps)

- 锁定时间:仅约400个参考时钟周期

- 分数分频输出:支持无毛刺快速频率切换,具备6bit分数分辨率,适用于动态频率调节(DVFS)

- 小型化设计:将模拟电路模块所占面积大幅减少,在GF22FDX 工艺下面积仅0.008mm2

- 可靠性:在工艺、电压、温度(PVT)极限条件下均可稳定工作

pPLL03 同时支持整数与分数N频率合成模式,可实现精细的频率调节。其全数字控制接口便于与标准数字设计 流程无缝集成,同时支持软件可配置控制,从而大幅提升设计灵活性与系统可编程性。

“我们在设计 pPLL03 时的目标,正是在如 GlobalFoundries 22FDX 这样的先进工艺节点上,实现同类 别产品中最佳的抖动性能与灵活的集成特性,”Perceptia Devices 首席技术官 Julian Jenkins 表示。 “目前的硅片实测数据有效的验证了我们的设计理念和开发流程,我们确信这款IP已经充分的满足了量 产条件。”

格芯(GlobalFoundries) 22FDX平台专为低功耗、高密度应用优化,典型应用领域涵盖移动设备、边缘AI、射 频通信与嵌入式处理。pPLL03目前以在此工艺上具备可用性,为客户提供了一种充分发挥FD-SOI特性优势的差异 化时钟解决方案。

pPLL03设计套件内容包括:

- Liberty(.lib)时序模型

- Verilog与Verilog-A仿真模型

- GDSII与LEF版图

- CDL网表

- 集成设计指南与版图约束说明

- 完整的IP验证数据

该设计套件目前已向满足条件的授权客户开放获取。如您需要了解授权详情或咨询其他产品,请联系 Perceptia Devices销售团队:sales@perceptia.com

关于pPLL03

pPLL03是一款专为先进工艺节点优化设计的紧凑型低抖动锁相环(PLL)IP核。该款IP输出频率范围可达 4GHz,其极佳的低抖动性能与优异的集成灵活性使其完美适配包括高性能计算、人工智能(AI)加速及时序敏感 逻辑在内的不同高性能高要求应用场景。pPLL03尤其适用于为多时钟域提供时钟。它帮助设计人员在不牺牲面积 或功耗的前提下,构建先进可靠的高性能时序架构。

关于Perceptia Devices

Perceptia Devices 总部位于澳大利亚悉尼,是行业领先的半导体 IP 和设计服务提供商。Perceptia 专注于 高速与超低功耗的混合信号芯片设计,致力于为无线通信、人工智能(AI/ML)、数据转换及混合信号 SoC 等多 领域客户提供时序精准、集成高效的解决方案。凭借深厚的技术积累和灵活的设计能力,Perceptia 在过去20余 年中助力客户加速产品开发,实现卓越性能。

如需了解更多产品信息或索取产品数据手册,您可以通过以下方式联系我们:

Related Semiconductor IP

- All Digital Fractional-N PLL for Performance Computing in GlobalFoundries 22FDX

- X-band (7.9 − 9.8GHz) High Performance Frac-N PLL

- Frac-N PLL on Samsung 28nm LN28FDS

- Frac-N PLL on Samsung 8nm LN08LPP

- Frac-N PLL on Samsung 4nm LN04LPP

Related News

- Perceptia 正式发布基于格芯(GlobalFoundries)22FDX 平台的 pPLL05 设计套件

- Perceptia 正式发布基于 GlobalFoundries 22FDX 的 10-bit 极低温 (Cryogenic)数/模(DAC)、模/数(ADC)转换器 IP

- Cadence全流数字工具套件获得格芯22FDX认证

- Dolphin Integration的功率调节IP,现已通过GLOBALFOUNDRIES 22FDX技术平台进行硅验证