AES IP

All offers in

AES IP

Filter

Compare

131

AES IP

from

41

vendors

(1

-

10)

-

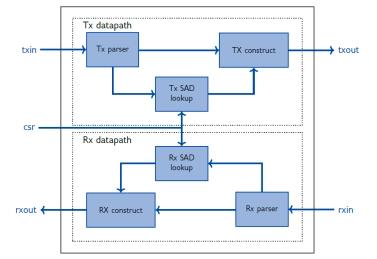

IPSEC AES-256-GCM (Standalone IPsec)

- XIP7213E implements the Internet Protocol Security (IPsec) as standardised in RFC4303 and RFC4305.

- The IPsec protocol defines a security infrastrucure for Layer 3 (as per the OSI model) traffic by assuring that a received packet has been sent by the transmitting station that claimed to send it.

-

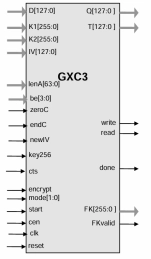

P1619 / 802.1ae (MACSec) GCM/XTS/CBC-AES Core

- Small size: From 70K ASIC gates (at throughput of 18.2 bits per clock)

- 500 MHz frequency in 90 nm process

- Easily parallelizable to achieve higher throughputs

- Completely self-contained: does not require external memory. Includes encryption, decryption, key expansion and data interface

-

AES-SX Secure Core - High-Throughput AES Core with Advanced SCA/FI Protection for Performance-Critical Systems

- The High-Performance AES IP core is a fast, silicon-proven cryptographic engine designed for systems with demanding encryption workloads.

- Built on a 20 S-box parallel architecture, it delivers exceptional AES-128/256 encryption and decryption throughput while supporting standard modes including ECB, CBC, and CTR (excluding GCM, XTS, and CBC-MAC).

-

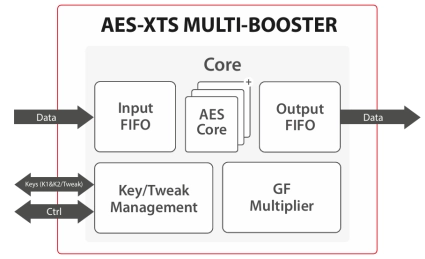

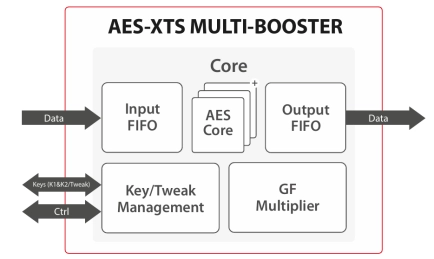

AES-XTS Multi-Booster

- The AES-XTS Multi-Booster crypto engine includes a generic & scalable implementation of the AES algorithm making the solution suitable for a wide range of low-cost & high-end applications (including key, tweak, input and output registers and Galois field multiplier).

-

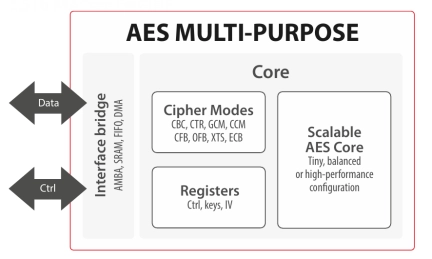

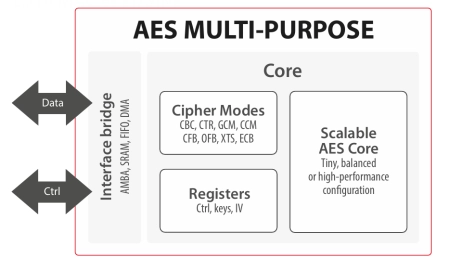

AES Mutli-Purpose crypto engine

- The AES Multi-Purpose crypto engine includes a generic and scalable implementation of the AES algorithm and a configurable wrapper making the solution suitable for a wide range of low-cost & high-end applications.

-

AES Multi-purpose crypto engine

- ASIC and FPGA

- Supports a wide selection of programmable ciphering modes based on NIST SP 800-38:

- Masking option available with excellent protection against SPA & DPA

- Context switching

-

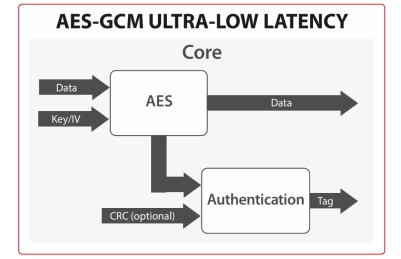

AES-GCM Ultra-low latency crypto engine

- The AES-GCM Ultra-low latency crypto engine is targeted for CXL link encryption with an implementation of the AES-GCM algorithm compliant with the NIST SP 800-38D standard.

- The unique architecture enables high throughput while maintaining an optimal resource usage.

-

AES-XTS Muti-Booster

- The AES-XTS Multibooster crypto engine includes a generic & scalable implementation of the AES algorithm making the solution suitable for a wide range of low-cost & high-end applications (including key, tweak, input and output registers and Galois field multiplier).

-

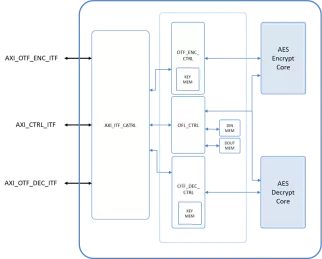

AES Engine IP

- The AES engine IP is a high-performance cryptographic engine operates in AES NIST Federal information processing standard FIPS-197.

- It supports AES-ECB AES-XTS mode and 128/256 key-length both encryption/decryption.

- The core engine supports 128/256/512 data width operation.

-

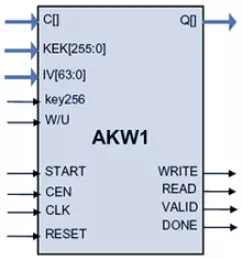

NIST AES Key Wrap/Unwrap Core

- Small size: AKW1 starts from less than 8,000 ASIC gates

- Completely self-contained: does not require external memory

- Supports both encryption (wrap) and decryption (unwrap). Encryption-only and decryption only versions available.

- Includes AES key expansion