Noise Monitor IP

Filter

Compare

36

IP

from

19

vendors

(1

-

10)

-

Low Power Fractional PLL IP in TSMC(12/16nm FFC, 22nm ULP/ULL, 28nm HPC+)

- Compact IP size ( smaller than 0.01mm²) and low power consumption ( < 2.7mW @ 3.5GHz )

- Compactible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter ( < +-15ps )

- Support 24-bit fractional accuracy

-

OSC Ring Oscillator Programmable Nano Power Series

- OSCILLATOR: The oscillator SGC21543 is a programmable ring oscillator optimized for ultra low power applications

- It as been optimized to work from 10 kHz to 10 MHz

- The and uses a current controlled ring oscillator topology to achieve both ultra low power consumption and high noise immunity

- For 32 kHz low precision RTC applications the SGC21543 can operate for weeks from the charge of a single super capacitor

-

OSC Ring Oscillator Programmable Nano Power Series

- OSCILLATOR: The oscillator SGC21543 is a programmable ring oscillator optimized for ultra low power applications

- It as been optimized to work from 10 kHz to 10 MHz

- The and uses a current controlled ring oscillator topology to achieve both ultra low power consumption and high noise immunity

- For 32 kHz low precision RTC applications the SGC21543 can operate for weeks from the charge of a single super capacitor

-

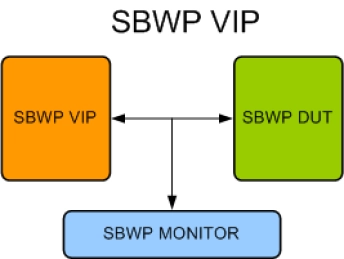

Safe-By-Wire Plus Verification IP

- Adherent to Safe-By-Wire Plus 2.0 Specification.

- Supports generation of frames with error and noise injection.

- Tracking of transmit and receive counters.

- Protocol Checker fully compliant with Safe-By-Wire Plus 2.0 specification.

-

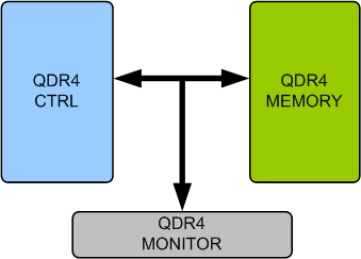

QDR4 Memory Model

- Supports QDR4 memory devices from all leading vendors.

- Supports 100% of QDR4 protocol standard CY7C4142KV13.

- Supports for 144-Mbit density (8M × 18, 4M × 36)

- Supports for Eight-bank architecture enables one access per bank per cycle

-

UCIe-S 64GT/s PHY IP

- The UCIe-S 64GT/s PHY IP is a cutting-edge solution designed to meet the growing demand for ultra-high-speed interconnects between dies in standard packaging environments.

- Leveraging the UCIe (Universal Chiplet Interconnect Express) 3.0 standard, this IP supports a blistering data rate of up to 64Gbps per lane, enabling next-generation AI, HPC, and data center SoC applications.

-

UCIe-A 64GT/s PHY IP

- The UCIe-A 64GT/s PHY IP is a cutting-edge solution designed to meet the growing demand for ultra-high-speed interconnects between dies in advanced packaging environments.

- Leveraging the UCIe (Universal Chiplet Interconnect Express) 3.0 standard, this IP supports a blistering data rate of up to 64Gbps per lane, enabling next-generation AI, HPC, and data center SoC applications.

-

PVT sensor integrated SAR ADC in 12nm

- 10bit 0.25Msps SAR ADC

- SNR:56dB@0.1Msps, 10KHz input signal.

- Multi single ended: 4 channels

- Temperature SENSER = TCPTAT=2.5mV/°C, ?T=±2°C

-

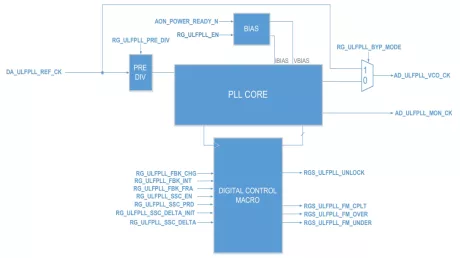

Fractional N Clock PLL

- High performance Fractional-N PLL

- Low power dissipation

- No external components required

- Integer Mode

-

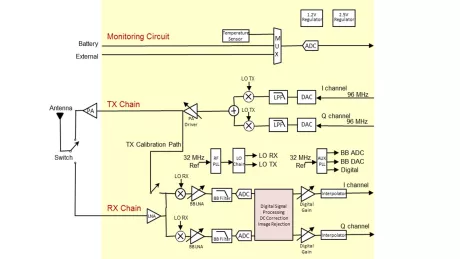

HaLow 802.11ah Transceiver for IoT

- The 802.11ah HaLow Transceiver meets the bandwidth and power consumption requirements of a new generation of IoT and mobile devices, where battery life and extended range are prerequisites for successful deployment.

- It meets the IEEE 802.11ah standard, known as Wi-Fi HaLow™.