NXP IP

Filter

Compare

35

IP

from

13

vendors

(1

-

10)

-

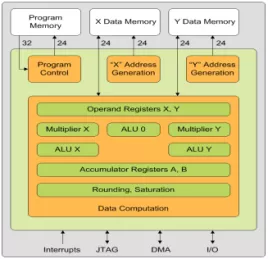

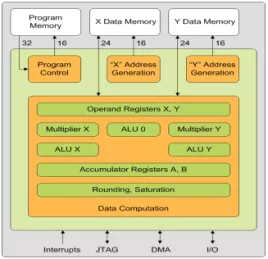

Ultra low power C-programmable Baseband Signal Processor core

- Ultra low power consumption

- Highly optimizing C-compiler software toolkit

- Minimal core size (65k gates), excluding debug interface (6k gates)

- Small memory footprint

-

Ultra low power C-programmable DSP core

- Ultra low power consumption

- Highly optimizing C-compiler software toolkit

- Minimal core size (43k gates), excluding debug interface (6k gates)

- Small memory footprint

-

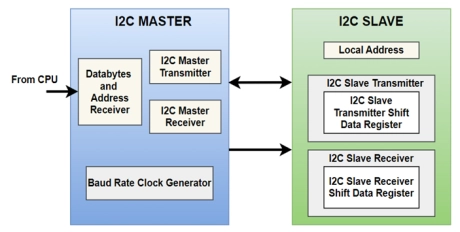

I2C - Function Controller

- The I2C (Inter - Integrated Circuit) protocol is a widely used serial communication protocol for transferring data between electronic devices. It was developed by Philips in the 1980s and is now owned by NXP Semiconductors. I2C uses two bidirectional data lines called SDA (Serial Data) and SCL (Serial Clock) for communication between devices.

- It allows multiple devices to be connected to the same bus, and each device can be identified by a unique address. The protocol supports data transfer rates ranging from a few kilobits per second to several hundred kilobits per second.

-

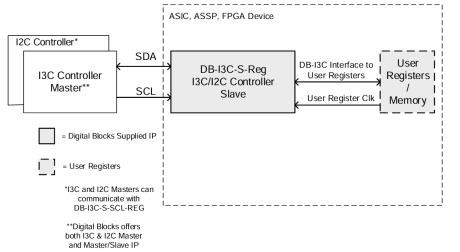

I3C Controller IP – I3C / I2C Slave, Configure User Registers, no CPU Host Required

- The DB-I3C-S-REG is an I3C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs requiring the configuration & control of registers with no local host processor.

- The DB-I3C-S-REG processes the I3C protocol & physical layers, and receives & transmits bytes with respect to the I3C payload to / from User Registers within an ASIC / ASSP / FPGA device.

- The DB-I3C-S-REG Controller implements the Slave-Transmit and Slave-Receive protocol according to the MIPI I3C-Basic-Spec ver1_0 specification.

-

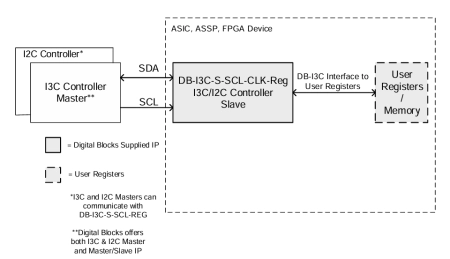

I3C Controller IP – I3C / I2C Slave, SCL Clock only, Configure User Registers, no CPU Host Required

- The DB-I3C-S-SCL-CLK-REG is an I3C Slave Controller IP Core focused on low power, low noise, low VLSI footprint ASIC / ASSP designs requiring the configuration & control of registers with no free running clock.

- The DB-I3C-S-SCL-CLK-REG processes the I3C protocol & physical layers, and receives & transmits bytes with respect to the I3C payload to / from User Registers within an ASIC / ASSP / FPGA device.

- The DB-I3C-S-SCL-CLK-REG Controller implements the Slave-Transmit and Slave-Receive protocol according to the MIPI I3C-Basic-Spec-ver1_0 specification.

-

UCIe based 8-bit 48-Gsps Transceiver (ADC/DAC/PLL/UCIe)

- 48-Gsps peak sample rate

- 8 bit resolution

- UCIe SP (16x lanes at 16Gbps) with streaming controller

-

UCIe based 12-bit 12-Gsps Transceiver (ADC/DAC/PLL/UCIe)

- 12-Gsps peak sample rate

- 12 bit resolution (programmable)

- UCIe SP (16x lanes at 16Gbps) with streaming controller

-

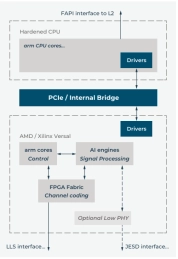

Modular, high performance 5G NR Layer 1 (PHY) solutions for Non-Terrestrial Network applications

- Complete implementation as per 3GPP standards and O-RAN SCF specifications.

- A full Layer 1 PHY designed and developed by AccelerComm™ using a mixture of hardware and software optimized to meet the needs of satellite vendors.

- Openly Licensable.

- Pre-integrated with AccelerComm™ LDPC and Polar encoder/decoder chains and inherits all the benefits from these highly performant products.

-

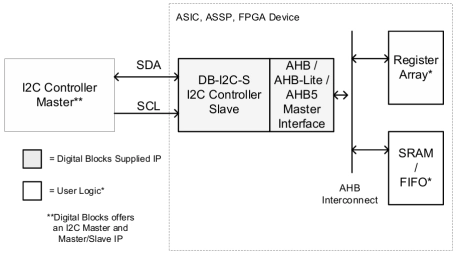

I2C Controller IP – Slave, Parameterized FIFO, AHB Master Interface (I2C2AHB)

- The DB-I2C-S-AHB-BRIDGE is an I2C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required), and an AHB Master interface for read/write to the user system.

- The DB-I2C-S-AHB-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via a bridge AHB Master Interface to user registers or memory.

-

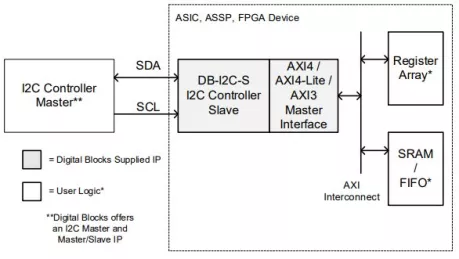

I2C Controller IP – Slave, Parameterized FIFO, AXI Master Interface (I2C2AXI)

- The DB-I2C-S-AXI-BRIDGE is an I2C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required), and an AXI Master interface for read/write to user system.

- The DB-I2C-S-AXI-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via the bridge AXI Master Interface to user registers or memory.