32-Bit Microprocessor IP

Welcome to the ultimate 32-Bit Microprocessor IP hub! Explore our vast directory of 32-Bit Microprocessor IP

All offers in

32-Bit Microprocessor IP

Filter

Compare

114

32-Bit Microprocessor IP

from

16

vendors

(1

-

10)

-

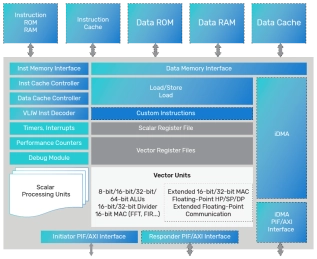

Tensilica ConnX 120 DSP

- Certified ISO 26262:2018 ASIL-compliant

- VLIW parallelism issuing multiple concurrent operations per cycle

- 256-bit SIMD

- Up to 64 MAC

-

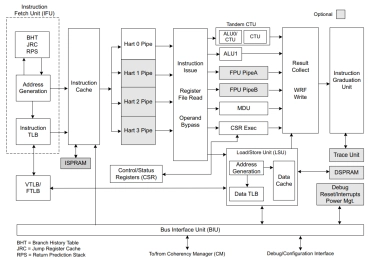

Data Movement Engine - Efficient data-processing and simultaneous multi-threading, low latency and deterministic data access

- Efficient throughput with the first RISC-V core to support up to 4-way multithreading

- Highly scalable multi-core, multi-cluster coherent computing solution

- MIPS Enhancements for increased connectivity and throughput

- Use in 5G/6G Comms Infrastructure, Automotive Gateways, Embedded & Datacenter

-

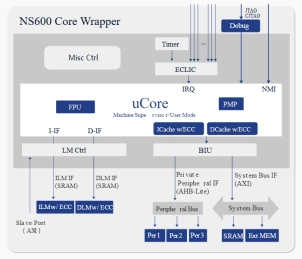

32-Bit Security processor

- Nuclei Security processor is a series of chips designed specifically for security application scenarios, including NS100, NS300, and NS600 products.

-

AI DSA Processor - 9-Stage Pipeline, Dual-issue

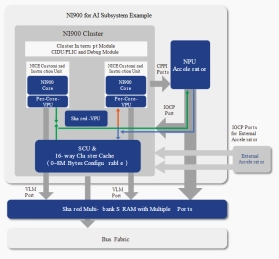

- NI900 is a DSA processor based on 900 Series.

- NI900 is optimized with features specifically targeting AI applications.

-

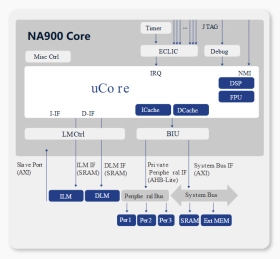

32-Bit Automotive Processor - 9-Stage Pipeline, Dual-issue

- NA900 series processor is the 1st ISO26262 ASIL-B/D Product Certified RISC-V CPU IP, Nuclei self-developed STL supports multiple ASIL-B automotive use cases.

-

32-Bit Automotive Processor - 3-Stage Pipeline, Single/Dual-issue

- NA300 series processor is a ISO26262 ASIL-B/D Certified RISC-V CPU IP,Nuclei self-developed STL supports multiple ASIL-B automotive use cases.

-

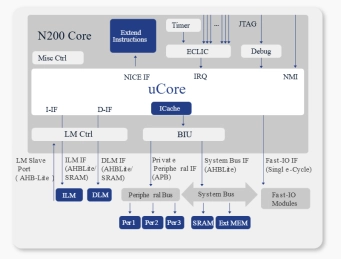

32-Bit Low Power Processor - 2-Stage Pipeline, Single-issue

- N200 Series is designed for deeply embedded application with low power and area consumption.

-

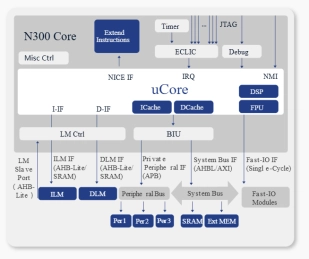

32-Bit High Efficiency Processor - 3-Stage Pipeline, Single/Dual-issue

- N300 Series is a 32-bit RISC-V processor designed for applications requiring extreme energy efficiency and DSP/FPU features.

- N300 Series can be applied to AIoT, embedded and industrial control, etc.

-

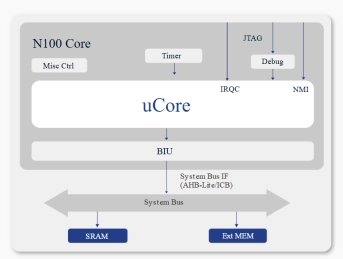

32-Bit High Performance Processor - 2-Stage Pipeline, Single-issue

- With extreme low area, N100 is a 32b RISC-V processor designed specifically for low power application.

- N100 aims for cost sensitive application including IoT, MCU, sensor.

-

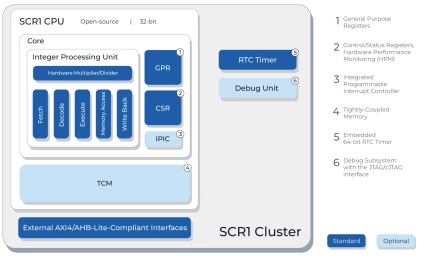

Open-source compact microcontroller core with a 4-stage in-order pipeline for deeply embedded applications

- SCR1 is an open-source and silicon-proven RISC-V-compatible, 32-bit, entry-level, MCU-class core. It targets general-purpose, deeply embedded applications and control systems.